|

|

|

|||||||

| Ответить в этой теме |  |

|

|

|

|

|

|

Опции темы | Поиск в этой теме |

|

|

|

|||||||

| Ответить в этой теме |  |

|

|

|

|

|

|

Опции темы | Поиск в этой теме |

|

|

#1 (ссылка) |

|

Crow indian

Регистрация: 21.02.2009

Возраст: 40

Сообщений: 29,902

Поблагодарил: 398 раз(а)

Поблагодарили 5984 раз(а)

Фотоальбомы:

2576 фото

Записей в дневнике: 698

Репутация: 126089

|

Тема: Спутниковые ресиверы DRE(DRS)-4500. Устройство и ремонтСпутниковые ресиверы DRE(DRS)-4500. Устройство и ремонт В. ФЁДОРОВ,г. Липецк Широкое распространение компанией НСК программ ’ Триколор ТВ~Центр” [ 1] на западной территории России подвигло её к продвижению передач на восток страны. В начале проекта "Триколор TB-Сибирь" использовали ресиверы DRE-5500 [2] с САМ-модулями системы DRE CRYPT, имеющие встроенный транскодер MPEG-2/MPEG-4. Но для снижения себестоимости было решено применить новые ресиверы DRE-4500 фирмы Digi Raum Electronics со встроенным транскодером, позволяющие устанавливать смарт-карты системы DRE CRYPT. Через несколько лет на смену DRE-4500 пришёл ресивер DRS-4500, выпускавшийся тайваньской фирмой DownRidge Select Limited, представлявшей собой правопреемницу Digi Raum Electronics. В публикуемой статье рассмотрены ресиверы DRE(DRS)-4500, их особенности и различия, методы диагностики неисправностей, возникающих при их эксплуатации, причины, приведшие к ним, и способы их устранения. Напомним, что по проекту "Триколор TB-Сибирь" НСК начала вещание 6 декабря 2007 г. на территории Урала, Сибири и части Дальнего Востока [1]. Для этого сначала использовали каналы спутника БОНУМ-1 в позиции 56° в. д. С целью вещания были арендованы два транспондера: 27 (12226,16 МГц) и 39 (12379,32 МГц) с левосторонней круговой поляризацией, а позже — дополнительно транспондер 35 (12379,60 МГц) с такой же поляризацией. Трансляцию вели в цифровом стандарте DVB-S. Поскольку к началу 2013 г. спутник БОНУМ-1 практически исчерпал свой ресурс, ФГУП "Космическая связь" совместно с компанией Intelsat обеспечили перевод американского спутника DIREC TV-1 R в позицию 55,8° в. д. Программы транслировали через транспондеры Т0019 (12486,44 МГц), Т0014 (12413,54 МГц) L, Т0016 (12442,70 МГц) L, Т0012 (12384,38 МГц) L, Т0010 (12355,22 МГц) L. Первый из них вещал с правой круговой, а остальные — с левой круговой поляризацией. Ввиду того что полоса пропускания транспондеров была 24 МГц (33 МГц у спутника БОНУМ-1), скорость потока уменьшилась до 21500 Мбит/с при свёрточном коде 3/4. В апреле 2014 г. спутник DIREC TV-1R, также практически отработавший свой ресурс, был замещён российским спутником ЭКСПРЕСС АТ-1, выведенным в ту же позицию 16 марта 2014 г. Программы стали транслировать через транспондеры ТР13 (11958 МГц), ТР15 (11996 МГц), ТР17 (12034 МГц), ТР19 (12073 МГц), ТР21 (12111 МГц), ТР23 (12149 МГц), ТР25 (12188 МГц), ТР27 (12226 МГц), ТР29 (12265 МГц), ТР31 (12303 МГц), ТРЗЗ (12341 МГц), ТР37 (12418 МГц), ТР39 (12456 МГц). Все они вещают с левой круговой поляризацией со скоростью потока 27500 Мбит/с при свёрточном коде 3/4. Для передачи через такое ограниченное число (13) транспондеров большого пакета телевизионных каналов (40) передачи ведутся по формату сжатия видеосигналов MPEG-4, который предоставляет более высокие коэффициенты сжатия, чем MPEG-2. Кодирование происходит в системе DRE CRYPT 2. С целью просмотра программ необходимо установить в ресивер оплаченную смарт-карту "Триколор ТВ-Сибирь". Модели DRE(DRS)-4500 (внешний вид показан в [1]) собраны почти по одинаковым схемам. Практически они отличаются входными NIM-модулями, узлами питания внешнего конвертера и коре-модулями (в их состав входит транскодер MPEG-2/MPEG-4). Они собраны в одинаковых корпусах, но с разными фирменными надписями на шильдиках передней панели. Эти цифровые ресиверы предназначены для приёма спутниковых телевизионных и радиовещательных программ, передаваемых по системе DVB-S. Они преобразуют цифровой входной сигнал в аналоговый сигнал цветного телевидения со стандартным разрешением SD (Standard Definition). Частоты входных сигналов, приходящих с конвертера, могут находиться в пределах 950... 2150 МГц и иметь уровень от -65 до -25 дБмВт. Приём может происходить по системам МСРС и SCPC (множество программ или одна программа на одной несущей соответственно). Ресиверы обеспечивают также приём сервисной информации, телетекста, субтитров. Память ресивера сохраняет настройки на' 5000 каналов. Для управления, настройки и установки параметров приёма используют меню экранной графики OSD и семидневное русифицированное навигационное меню EPG. Для управления внешними устройствами, коммутирования конвертеров применён интерфейс, работающий по протоколам DiSEqC 1.0—1.2 (USALS). Ресиверы имеют выходы CVBS (разъёмы RCA-JACK или организации просмотра программ в студийном качестве). Обновление программного обеспечения (ПО) ресиверов происходит с хост-компьютера, снабжённого последовательным интерфейсом RS-232. Также имеется возможность OTA (Over То Air) — обновления со спутника. Потребляемая мощность от сети переменного напряжения 190...250 В при частоте 50/60 Гц — не более 20 Вт. Допустимая рабочая температура — 5...40 °С. Размеры — 260x50x180 мм. Масса — не более 1,4 кг. Кроме приёма открытых (FTA — Free То Air) каналов, ресиверы позволяют при использовании декодера, входящего в состав коре-модуля, просматривать кодированные каналы, скремблированные в системах DRE CRYPT 2 и BISS (Mode 1 с памятью на семь фиксированных ключей). Кодировка DRE CRYPT 2 внедрена в проекте "Триколор ТВ", а систему BISS широко используют российские государственные спутниковые вещатели.  У ресиверов отсутствует С1-интер-фейс (Common Interface) общего назначения для установки САМ-модулей. Поэтому просмотр программ, кодированных по другим системам криптографии, невозможен.  Несмотря на то что в настоящее время описываемые ресиверы официально сняты с производства, в восточной части России и странах Средней Азии имеется большой (несколько сот тысяч) парк этих аппаратов, и они по-прежнему рекомендуются НСК. Хотя компания настоятельно предлагает заменить их на современные ресиверы, имеющие расширенные функциональные возможности, она продолжает программно поддерживать их и модернизировать ПО.  Структурная схема ресиверов показана на рис. 1. Входной сигнал с наружного конвертера поступает на NIM-модуль. В ресиверах DRE-4500 использован модуль BS2F7VZ0194А, а в ресиверах DRS-4500 — модуль EDS-1547FF1В + , описанный в [2]. NIM-модуль BS2F7VZ0194A содержит микросхему РЧ-преобразователя-селектора каналов IX2476VA фирмы Sharp. Она обеспечивает настройку ресивера на несущую частоту требуемого канала и преобразует входной сигнал (при нулевой ПЧ), выделяя из него составляющие I и Q. В модуле BS2F7VZ0194A сигналы I и Q проходят с РЧ-преобразователя на QPSK-демодулятор STV0299B фирмы ST Microelectronics. В нём происходит стандартная демодуляция QPSK-сигна-лов со скоростями потока 2...45 Мбит/с. Для коррекции ошибок в декодере свёрточный код Виттерби может принимать весь ряд стандартных значений: 1/2, 2/3, 3/4, 5/6, 7/8 (при длине кодового ограничения К = 7). Кроме того, демодулятор обеспечивает деперемеже-ние сигнала и декодирование кодов Рида-Соломона с коррекцией ошибок. Выходной транспортный поток Transport Stream (TS) дерандомизируется и нормализуется согласно нормам стандарта DVB-S и поступает на выход NIM-моду-ля.  С целью изменения поляризации конвертера использован метод инжекции в кабель снижения постоянного напряжения разных значений, служащего одновременно для питания конвертера: 13±0,5 В (вертикальная) или 18±0,5 В (горизонтальная). Потребляемый ток не должен превышать 0,5 А. В случае его превышения срабатывает защита и программно сообщается об этом пользователю. Поддиапазоны Ku-диапазона переключают путём подачи в кабель снижения синусоидального немодулиро-ванного сигнала частотой 22±4 кГц и амплитудой 0,6±0,2 В. Внешними дополнительными устройствами (поворотными механизмами, переключателями конвертеров) управляют инжектированием в кабель снижения команд, сформированных на основе протоколов DiSEqC 1.0—1.2 (USALS). С выхода NIM-модуля сигналы TS в формате MPEG-4 или MPEG-2 приходят на коре-модуль, выполненный на микросхеме AVC-декодера NP4 или NP4+. Он связан с многофункциональным однокристальным декодером в процессоре STi5518BQC семейства Omega. Его основой служит микроконтроллер ST20, управляющий функционированием всего ресивера. Сигналы TS проходят либо через транскодер MPEG-4/ MPEG-2 коре-модуля и затем на процессор, либо поступают непосредственно на процессор, если приняты передачи, сжатые по системе MPEG-2. Для связи AVC-декодера и микросхемы STi5518BQC использована технология клиент-сервер по принципу работы CAM-модулей. О коре-модуле подробнее будет рассказано ниже. Скремблированный сигнал обрабатывается DES-дескремблером в микросхеме NP4 или NP4+. При приёме FTA-программ роутер потока в микросхеме направляет сигнал непосредственно на выход коре-модуля, в обход DES-дескремблера. В ресивере имеется слот картридера, обменивающегося данными со смарт-картами посредством интерфейса, соответствующего стандарту ISO 7816. Интерфейс связан с дескремблером системы условного доступа DRE CRYPT в микросхеме NP4 или NP4+.  С выхода коре-модуля сигналы TS попадают на однокристальный деко- дер STi5518BQC, который обрабатывает их согласно спецификации MPEG-2 ISO/IEC 13818 при входной скорости до 60 Мбит/с. Они демультиплексируются им, выделяя требуемый телевизионный или радиовещательный канал, а также сигналы сервисной информации. Полученные сжатые пакеты сигналов видеоизображения и звука со скоростями до 15 Мбит/с декодируются MPEG-декодером (MPEG-2 MP@ML ISO/IEC 13818). С его выхода цифровой несжатый видеосигнал в формате 4:3 или 16:9 (720 пкс на 576 строк при частоте полей 50 Гц), преобразованный DENC-кодером, проходит на буферные выходные усилители, выполненные на дискретных элементах. Цифровой несжатый сигнал звукового сопровождения поступает на выходные усилители через ЦАП HT82V731 фирмы Holtek. С ресиверов можно снимать как композитный видеосигнал ПЦТВ (разъёмы RCA и SCART), так и компонентные RGB (SCART) и Y/C (S-Video). Аналоговые сигналы звукового сопровождения выведены как на RCA-, так и на SCART-разъёмы, а цифровые — через оптический S/P-DIF-вы-ход. Обновление ПО с хост-компьютера обеспечивается через последовательный интерфейс RS-232. Преобразование уровней интерфейса в рабочие уровни процессора происходит в узле на дискретных элементах. Ресиверы DRE(DRS)-4500 собраны на пяти печатных платах: основной, криптомодуля, картридера, управления и источника питания. Внешний вид основной платы МВ-08 rev.2.01, применённой в ресивере DRE-4500, показан на рис. 2, а принципиальная схема — на рис. 3. Последняя разделена на четыре части. Обратите внимание на то, что часть рис. 3.3 помещена рядом с рис. 3.1. ЛИТЕРАТУРА 1. Фёдоров В. "Триколор ТВ" — общедоступное телевидение. — Радио, 2013, №3, с. 8-10. 2. Фёдоров В. Спутниковые ресиверы DRE-5000/5500, DRS-5001/5003 и GS-7300. Устройство и ремонт. — Радио, 2014, № 2, с. 8— 13; №3,с. 8—10; № 4, с. 7— 11; № 5, с. 7—11. (Продолжение следует) Последний раз редактировалось Admin; 23.05.2015 в 00:41. |

|

|

Цитировать 12 |

| Поблагодарили: |

Данный пост получил благодарности от пользователей

|

|

|

#2 (ссылка) | |

|

Super V.I.P.

Регистрация: 16.02.2012

Сообщений: 5,262

Поблагодарил: 6718 раз(а)

Поблагодарили 977 раз(а)

Фотоальбомы:

не добавлял

Репутация: 1694

|

Цитата:

|

|

|

|

Цитировать 0 |

|

|

#3 (ссылка) |

|

Super V.I.P.

Регистрация: 26.09.2010

Возраст: 46

Сообщений: 4,304

Поблагодарил: 199 раз(а)

Поблагодарили 682 раз(а)

Фотоальбомы:

13 фото

Репутация: 945

|

После того как в плате блока питания образуется обугленная дырка (года 3 - 4), выбрасываем почти всю горячую часть, и ставим микросхему 5L038 _))

|

|

|

Цитировать 0 |

| Поблагодарили: |

Данный пост получил благодарности от пользователей

|

|

|

#4 (ссылка) |

|

Crow indian

Автор темы Регистрация: 21.02.2009

Возраст: 40

Сообщений: 29,902

Поблагодарил: 398 раз(а)

Поблагодарили 5984 раз(а)

Фотоальбомы:

2576 фото

Записей в дневнике: 698

Репутация: 126089

|

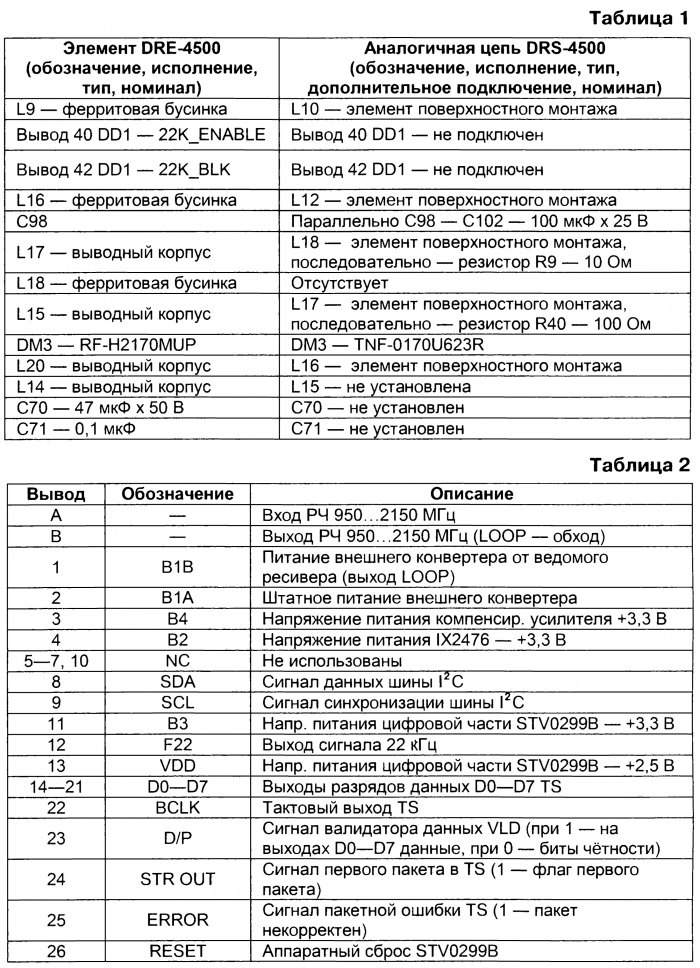

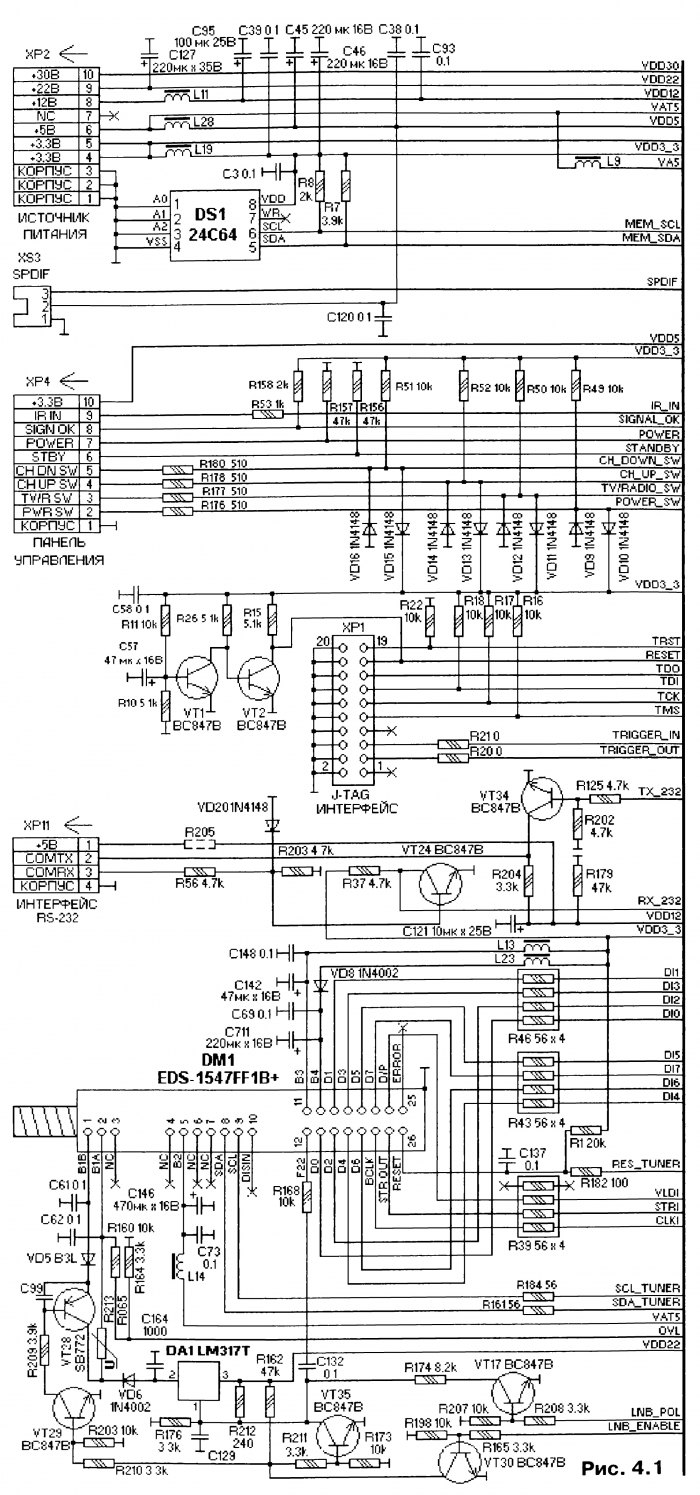

Продолжение

Принципиальная схема основной платы МВ-08 rev. 1.02, применённой в ресивере DRS-4500, очень похожа на схему платы ресивера DRE-4500, представленную в предыдущем номере. Поэтому здесь изображена только наиболее отличающаяся первая часть — рис. 4.1. Различия остальных частей схем перечислены в табл. 1. В ресивере DRE-4500 использован NIM-модуль BS2F7VZ0194A, выпускавшийся фирмой Sharp. Одно из направлений её деятельности — разработка NIM- и HALF-NIM-модулей для ресиверов стандартов DVB-S/S2/CA ABS-S, ATSC, ISDB-T, DTMB и для цифровых телевизоров. Внешний вид модуля показан на рис. 5, а вид без экранирующей крышки — на рис. 6. Установка в нём широко распространённых микросхем позволила создать высококачественное устройство, применявшееся в огромном числе цифровых ресиверов различных мировых производителей. В настоящее время модуль снят с производства.  Структурная схема модуля дана на рис. 7. Сигнал с внешнего понижающего частоту конвертера поступает через входной F-разъём на компенсирующий усилитель, собранный на СВЧ-транзис-торе 2SC5753 фирмы California Eastern Laboratories. Усиленный сигнал ответвляется на выходной разъём LOOP модуля для подключения дополнительного ресивера. Одновременно он приходит на РЧ-преобразователь с "нулевой" ПЧ, выполненный на микросхеме IX2476VA (маркировка производителя на корпусе — В0010). В её состав входят система АРУ, смесители I и Q с программно регулируемыми фильтрами НЧ, гетеродин с петлёй ФАПЧ. Микросхема работает с входными цифровыми сигналами стандарта DVB-S в интервале частот 950...2150 МГц, передаваемыми с символьной скоростью от 1 до 45 Мсимв/с. На входе микросхемы включён регулируемый усилитель, обеспечивающий широкий диапазон регулировки для работы с входными сигналами различных уровней. Монолитный гетеродин имеет малые уровни побочных излучений, а его частота стабилизирована кварцевым генератором и петлёй ФАПЧ. Колебания образцовой частоты через буферизированный выход синхронизируют QPSK-демодулятор. Управление устройствами РЧ-преобра-зователя происходит по интерфейсу 12С фирмы Philips (NXP) от управляющего процессора ресивера через 12С-ре-питер (ретранслятор), входящий в состав QPSK-демодулятора. Микросхему IX2476VA выпускают в 48-вывод-ном корпусе TQFP.  Сигналы составляющих I и Q с выхода микросхемы IX2476VA поступают на АЦП в QPSK-демодуляторе STV0299B. Сдвоенный АЦП преобразует их в шестиразрядную цифровую форму с частотой дискретизации до 90 МГц. Микросхема, кроме стандарта DVB-S, позволяет декодировать сигналы стандарта DSS (DIRECTV™). Поэтому оцифрованные сигналы после интерполятора проходят цифровой косинусквадратич-ный фильтр Найквиста с коэффициентами скругления 0,35 и 0,2. В демодуляторе имеются две петли цифровой АРУ. Первая из них управляет коэффициентом усиления входного РЧ-преобразователя, а вторая воздействует на внутренние исполнительные цепи. Из полученного сигнала восстанавливаются тактовые импульсы, которые синхронизируют работу узлов преобразования QPSK-сигналов в транспортный поток TS. Микросхема, используя находящийся в её составе порт ввода и вывода, может обеспечивать переключение питания конвертера и диапазонов приёма, а также инжектировать в кабель снижения сигналы системы DiSEqC. Однако в этом NIM-модуле такая функция не использована. Источник питания конвертера на рисунке показан условно и не входит в состав модулей. Он собран на отдельной специализированной микросхеме в ресивере DRE-4500 и на дискретных элементах в DRS-4500. Параметры приёма QPSK-сигналов устанавливаются по шине 12С, обслуживаемой процессором ресивера и работающей на частотах до 4 МГц. Микросхема имеет режим репитера, при котором сигналы шины 12С от центрального процессора пересылаются на дополнительную шину, работающую на частотах до 400 кГц. По дополнительной шине возможно управление другой микросхемой в ведомом режиме. В нашем модуле это РЧ-преобразователь. Микросхема STV0299B была спроектирована в 2000 г. Её выпускали в 64-вы-водном корпусе TQFP. Для её питания используются два напряжения: 3,3 В — для интерфейсов ввода и вывода, а также 2,5 В — для аналоговой части входного АЦП и ядра.  Модуль BS2F7VZ0194А обеспечивает приём сигналов системы DVB-S с входным уровнем в интервале -65...-25 дБм и символьной скоростью от 2 до 45 Мбит/с и преобразовывает их в транспортный поток TS. Свёрточный декодер Виттер-би внутреннего кода обрабатывает ошибки со значениями 1/2, 2/3, 3/4, 5/6, 7/8 с длиной кодового ограничения К = 7. Контроль пакетных ошибок и их исправление происходят в декодере внешнего кода Рида-Соломона. Функционирование модуля возможно при температуре 0.. .60 °С (температура хранения 20...+85°С) и влажности не более 85 % (при хранении не более 95 %). Обозначение выводов модуля и их функциональное назначение указаны в табл. 2. Масса модуля — 35 г. Для работы модулей необходимы напряжения 3,3 ± 0,165 и 2,5 ± 0,125 В. Потребляемый от источников ток не превышает 200 и 350 мА соответственно. Для устойчивости входных цепей линия 3,3 В подключена через помехоподавляющий фильтр к отдельному стабилизатору напряжения. Принципиальная схема NIM-модуля BS2F7VZ0194A (преобразователя РЧ и QPSK-демодулятора) показана на рис. 8. Входной сигнал ПЧ с внешнего конвертера проходит через разъём на усилитель, компенсирующий затухание сигнала в соединительном кабеле снижения. Он собран на СВЧ-транзисторе VT1. Усиленный сигнал с выхода усилителя поступает через симметричный делитель-трансформатор на элементах L8, L9, R8 на выходной разъём (петля обхода для подключения второго ресивера) и на РЧ-преобразователь D1. ФНЧ на элементах L1 L4, С4С6, С8 С13 препятствует проникновению СВЧ-колеба-ний в цепи питания модуля. Сигнал гетеродина необходимой частоты формируется в микросхеме D1 с использованием петли ФАПЧ. Она определяет частоту принимаемого канала, а её установка обеспечивается по шине 12С. Первая петля АРУ состоит из детектора и усилителя-формирователя в QPSK-демодуляторе D2, а также исполнительного усилителя, управляемого напряжением, в микросхеме D1. Система АРУ поддерживает размах сигналов I и Q на выходе преобразователя РЧ на постоянном уровне при изменении входного сигнала в широком диапазоне. Микросхема D1 управляется по шине 12С через репитер, находящийся в демодуляторе D2. Работа узлов микросхемы D1 синхронизирована образцовым генератором, стабилизированным кварцевым резонатором BQ1. Эти же колебания синхронизируют и GPSK-демоду-лятор в D2. Сигналы I и Q с выхода РЧ-преобра-зователя D1 поступают на микросхему D2, преобразующую их в транспортный сигнал TS. Входной сигнал оцифровывается внутренним сдвоенным АЦП, восстанавливаются несущая и тактирующие импульсы. Делитель R24—R26 задаёт интервал напряжений, в котором происходит преобразование входных сигналов. После АЦП цифровой сигнал проходит цепи компенсации смещения постоянной составляющей, вносимой во входные сигналы РЧ-преобразователем. На выходе компенсатора установлен детектор первой петли АРУ, управляющей регулируемым входным усилителем РЧ-преобразователя D1. Оцифрованные сигналы последовательно проходят фильтр Найквиста, интерполятор, вторую внутреннюю петлю цифровой АРУ, а также декодер Виттерби, цепи депере-межения по Форни и декодер Рида-Соломона. После корректирования ошибок сигнал обрабатывается в компенсаторе энергетической дисперсии и в синхроинверторе. Полученный транспортный сигнал TS с выхода микросхемы поступает на выход NIM-модуля. Соответствующие узлы микросхемы D2 оценивают качество принимаемого канала, которое записывается в её регистрах. Управление её узлами происходит по шине гС. Использование репитера шины в микросхеме D2 уменьшает число управляющих линий для контроля над микросхемами D1 и D2 с четырёх до двух. Ядро GPSK-демодулятора D2 модуля питается напряжением +2,5 В, а периферийные устройства — напряжением +3,3 В. Подача питающих напряжений на микросхему происходит по правилу, при котором первым поступает напряжение +2,5 В, а затем — +3,3 В. Выключение питающих напряжений должно быть в обратной последовательности. Управление микросхемой IX2476VA (D1) обеспечивается стандартным управляющим интерфейсом 12С. Он функционирует на рабочих частотах до 400 кГц в режиме fast mode. У микросхемы имеются четыре управляющих адреса. Их выбирают аппаратно, подавая необходимое постоянное напряжение на вывод ADR (ADRess select) согласно табл. 3. Такая функция предназначена для управления несколькими модулями в мультипрограммных применениях. В описываемом модуле адрес микросхемы для записи равен COh, для чтения — C1h. Частота гетеродина, параметры петли ФАПЧ и другие настройки микросхемы обеспечиваются при пересылке по шине 12С пяти байт данных в соответствии с табл. 4 при установленном в 0 бите RTS в формате l2Sstart -> БАЙТ1 -> БАЙТ2 -> БАЙТЗ -> БАЙТ4 -» БАЙТ5, где БАЙТ1 — адрес микросхемы IX25765VA. При чтении микросхемы на неё отправляют адреса с флагом чтения. В ответ микросхема выдаёт на шину 12С байт, содержащий значения регистра состояния. Он предназначен только для чтения. Управляющие регистры доступны как для записи, так и для чтения. Необходимая частота гетеродина, представляющего собой генератор, управляемый напряжением (ГУН), и охваченного петлёй ФАПЧ, обеспечивается так. Колебания гетеродина делятся СВЧ-преска-лером с коэффициентом деления Р (16 или 32). После прескалера включён поглощающий счётчик с устанавливаемыми коэффициентами фиксированного N и переменного А делений в интервалах 5—255 и 0—31 (при А < N). Частота полученного сигнала сравнивается с частотой колебаний образцового генератора Fosc, делённой на коэффициент R. Напряжение ошибки воздействует на управляющий вход ГУН, стабилизируя его частоту. Частоту ГУН вычисляют по формуле FrYH = [(P*N) + A]*Fosc/R. Коэффициент деления Р прескалера переключают битом PSC. При значении 0 бита коэффициент равен 32, при установке бита в 1 — 16. Коэффициенты деления поглощающего счётчика N и А устанавливают битами N8—N1 и А5—А1 соответственно. Значения N меньше пяти запрещены. Коэффициент деления R частоты образцового генератора переключают битом REF. В случае значе- ния 0 бита коэффициент равен 4, значение 1 бита соответствует коэффициенту 8. При частоте генерации кварцевого резонатора 4 МГц частота сравнения будет равна соответственно 1 МГц и 500 кГц. Биты DIV, ВА2, ВА1, В АО служат калибровочными для ГУН (устанавливают интервал частот генерации выходного сигнала): 1110 — 950... 1065 МГц; 1111 — 1065...1170 МГц; 0001 — 1170...1300 МГц; 0010— 1300...1445 МГц; 0011 — 1445.. 1607 МГц; 0100 — 1607...1778 МГц; 0101 — 1778...1942 МГци 0110 —1942... 2150 МГц. Биты С1, СО определяют ток подкачки управляющей цепи в петле ФАПЧ (значение по умолчанию — ±1200 мкА): при 00 — ±120 мкА, 01 —±260 мкА, 10 — ±555 мкА, 11 —±1200 мкА. усилителя устанавливают битами BG1 и BG0. При значении 00 или 01 коэффициент равен 0 дБ, при 10 2 дБ, при 11 4 дБ. Биты PD5, PD4, PD3, PD2 определяют полосу пропускания выходных ФНЧ составляющих 6 и I выходного сигнала QPSK. Полоса пропускания ФНЧ по уровню -3 дБ принимает значения от 10 до 30 МГцс шагом 2 МГц при изменении значений битов от 0011 до 1101. При установке бита RTS в 0 микросхема функционирует в обычном режиме, а при значении 1 переходит в тестовый. Контрольные биты регистра состояния предназначены для чтения. Бит POR в значении 0 свидетельствует о том, что на микросхему подано нормальное напряжение питания (более 2,2 В), а все регистры установлены по умолчанию. Значение 1 этого бита сигнализирует о том, что напряжение питания ниже нормы, а микросхема не функционирует. Бит FL контрольного регистра определяет захват требуемой частоты петлёй ФАПЧ. Если он имеет уровень 0, петля ФАПЧ находится в состоянии захвата. При значении 1 этого бита система находится в режиме ошибки. Микросхема STV0299B имеет управляющий адрес для записи D0h, а для чтения — D1h. Как было указано выше, в ресиверах DRS-4500 применён модуль EDS-1547FF1B+, который подробно описан в [2]. В ресивере DRE-4500 (см. рис. 3) напряжение питания конвертера (и, следовательно, напряжение поляризации приёма) формирует микросхема DD5 LNBP13A фирмы ST Microelectronics, разработанная ещё в сентябре 1998 г. и предназначавшаяся для работы как в снимаемых в то время с эксплуатации аналоговых ресиверах, так и во внедрявшихся цифровых. Кроме указанной функции, микросхема обеспечивает инжекцию в кабель снижения сигнала 22 кГц для переключения поддиапазонов приёма, а также передачу в него сигналов протокола DiSEqC, формируемых QPSK-демодулятором NIM-модуля. Микросхемой DD5 управляет процессор в составе DD1 по трём линиям: разрешение подачи напряжения питания на конвертер EN, выбор поляризации VSEL (0 — напряжение питания конвертера 13 В, 1 — 18 В), разрешение прохождения сигнала 22 кГц ENT (при 1). В случае превышения внешним конвертером потребляемого тока или коротком замыкании в кабеле снижения транзистор VT24 закрывается, а процессор определяет состояние аварии в кабеле. Ресивер построен так, что при его переводе в дежурный режим управление поляризацией конвертера и переключение поддиапазонов приёма может обеспечиваться от второго ведомого ресивера. Однако при полностью выключенном основном ресивере питание с конвертера тоже снимается и функционирование ведомого ресивера нарушено, что, конечно, представляется недостатком такого соединения. В ресивере DRS-4500 напряжение питания конвертера и, следовательно, поляризации приёма формируется узлом, собранным на транзисторах VT17, \Я28— VT30, VT35 и микросхеме регулируемого линейного стабилизатора напряжения DA1 основной платы (см. рис. 4.1). Управление узлом питания конвертера и контроль над ним обеспечиваются процессором в однокристальном декодере DD1 по двум линиям: разрешение подачи напряжения питания на конвертер LNB ENABLE (через ключи на транзисторах VT30, VT35) и выбор поляризации LNB POL (ключ на транзисторе VT17). При превышении конвертером потребляемого тока или коротком замыкании в кабеле снижения напряжение на делителе R160R164 уменьшается, процессор считывает состояние аварии в соединении. При переключении ресивера в дежурный режим управление поляризацией конвертера и переключение поддиапазонов, как и в DRE-4500, может происходить от ведомого ресивера. Транзисторы VT28, VT29 обеспечивают прохождение на конвертер напряжения питания от ведомого ресивера (13 или 18 В). В рабочем режиме основного ресивера прохождение напряжения от ведомого блокировано. При полностью выключенном из сети основном ресивере питание с конвертера снимается, и функционирование ведомого ресивера нарушено. Через цепочку R168C132 в кабель снижения инжектируется сигнал 22 кГц (для переключения поддиапазонов приёма) и сигналы протокола DiSEqC, формируемые QPSK-демодулятором в NIM-модуле. Управление РЧ-преобразователем и QPSK-демодулятором модуля DM1 в ресиверах происходит по сепаратной шине 12С от процессора DD1.  Цифровые части ресиверов DRE-4500 и DRS-4500 подобны. Сигнал TS в стандарте MPEG-4 или MPEG-2 с выхода модуля DM1 (см. рис. 3 и 4.1) через ограничивающие резисторные сборки R39, R43 и R46 поступает на коре-модуль, устанавливаемый в коннектор XS4 (SO DIMM 144). Коре-модуль работает по принципу CAM-модулей в режиме клиент-сервер. При этом он использует ресурсы основного процессора DD1. О коре-модулях будет рассказано дальше. Элементы микросхем DD3, DD4, DD6, DD7 обеспечивают интерфейс доступа коре-модуля к ресурсам декодера DD1. Коммутатором управляет процессор в DD1. Дескремблированный поток TS передаётся с выхода коре-модуля на вход TS-роутера в DD1 при приёме кодированных программ или непосредственно роутером микросхемы NP4 (или NP4+) в коре-модуле с выхода NIM-модуля на TS-роутер DD1 при приёме FTA-каналов или каналов, кодированных в стандарте MPEG-2. Ресивером управляет 32-разрядный микроконтроллер ST20, служащий ядром процессора DD1. Его EMI-интерфейс использует параллельную FLASH-na-мять DS2 объёмом 16 Мбит, в которую записана управляющая программа. Памятью служит микросхема M29W160ET фирмы ST Microelectronics. Изменение управляющей программы ресиверов возможно через интерфейс RS-232. При этом модификация загрузчика (ВООТ-секторов) не происходит. Сопряжение уровней интерфейса RS-232 и портов ввода и вывода процессора DD1 обеспечивается каскадами на элементах VT28—VT30, VD13, VD15 (см. рис. 3) и VT24, VT34, VD20 (см. рис. 4.1). Если необходимо полностью перезаписать (модифицировать) содержимое DS2 (в том числе и ВООТ-секторы), используют метод программирования FLASH-памяти через JTAG-интерфейс. Он представляет собой 20-выводный штырьковый разъём ХР1 (завод-изготовитель на плате его не устанавливал). К 16-битному SMI-интерфейсу в процессоре DD1 подключено динамическое ОЗУ DS3 с объёмом памяти 64 Мбит (микросхема K4S641632K-UC60 фирмы Samsung). Она используется MPEG-2-де-кодером, управляющим процессором и цифровым кодером (DENC) в DD1. Образцовые колебания частотой 27 МГц вырабатываются задающим генератором, управляемым напряжением (ГУН). Он собран на микросхеме DD2. Частоту стабилизирует кварцевый резонатор ZQ1. Из образцовой частоты внутренние узлы процессора DD1 формируют частоты для работы ядра, других внутренних узлов, внешней FLASH- и SDRAM-памяти. При включении установку в исходное состояние (сброс) ресивера обеспечивает узел на транзисторах VT1, VT2. Аппаратный сброс при ремонте можно сделать, кратковременно замкнув выводы конденсатора С57 между собой. Микросхема ЭСПЗУ DS1 (24С64 фирмы ATMEL) сохраняет текущие настройки пользователя. Её связь с основным контроллером происходит по основной шине 12С.  Цифровые сигналы звукового сопровождения телевизионных программ поступают на звуковой ЦАП DA5, где они преобразуются в аналоговые сигналы. Аналоговые видео- и звуковые сигналы приходят на активные буферные усилители. Аналоговый полный цветной телевизионный сигнал обрабатывается усилителем на транзисторах VT6, VT8 и проходит на разъём SCART и РЧ-модулятор DM3 (RF-H2170MUP фирмы Wittis в DRE-4000 и TNF-0170U623R фирмы Tenas в DRS-4500). Компонентные сигналы R через усилитель на транзисторах VT9, VT11, G на VT16, VT20 и В на VT15, VT19 вместе со звуковым стереосигналом, прошедшим ФНЧ второго порядка DA4 и буферные усилители на транзисторах VT13, VT14, также поступают на разъём SCART. Суммированный сигнал стереоканалов через буферный усилитель на транзисторе VT18 подан на РЧ-модуля-тор, который переносит сигналы изображения и звукового сопровождения на любой канал ДМВ. Управление модулятором происходит по основной шине 12С. Буферные усилители на транзисторах VT5 и VT7, VT10 и VT12 согласуют выхо- ды компонентных сигналов Y и С микросхемы DD1 и разъём S-VIDEO XS2. Как было указано выше, для дескремблирования передач, шифрованных в системе DRE-CRYPT, и транскодирования аудио- и видеосигналов, кодированных в стандарте MPEG-4, в сигналы по системе MPEG-2 применяют коре-мо-дуль. Условный доступ обеспечивается при использовании смарт-карты, которую устанавливают в картридер, подключаемый к разъёму ХРЗ основной платы. Схема узла изображена на рис. 9. Карта принимает от микросхемы NP4 или NP4+ коре-модуля кодированные CW (Cipher Word) CSA ключи и выдаёт дешифрованные DW (Decipher Word) ключи. Согласование уровней интерфейса смарт-карты ISO-7816 и микросхемы NP4 или NP4+ обеспечивается в специализированной микросхеме коре-модуля. В ресиверах DRE-4500 применены коре-модули с использованием AVC-де-кодера NP4, а в ресиверах DRS-4500 — микросхемы NP4+. ПО обоих ресиверов может работать с любым коре-модулем на основе этих микросхем. (Продолжение следует) Последний раз редактировалось Admin; 27.05.2015 в 08:29. |

|

|

Цитировать 12 |

| Поблагодарили: |

Данный пост получил благодарности от пользователей

|

|

|

#5 (ссылка) |

|

Робот

Регистрация: 05.05.2009

Сообщений: 2,487

Поблагодарил: 0 раз(а)

Поблагодарили 82 раз(а)

Фотоальбомы:

не добавлял

Репутация: 0

|

Тема: Тема перенесена |

|

|

Цитировать 0 |

|

|

||||

| Тема | Автор | Раздел | Ответов | Последнее сообщение |

| =Диплом= Устройство и ремонт БВП-5 | Admin | Студенту-локомотивщику | 3 | 10.04.2020 11:05 |

| =Диплом= Устройство и ремонт ЭПК-150 | Admin | Студенту-локомотивщику | 1 | 05.01.2016 12:41 |

| =Диплом= Устройство и ремонт токоприемника П5 | Admin | Студенту-локомотивщику | 1 | 11.12.2015 16:22 |

| =Диплом= Устройство и ремонт резисторов | Admin | Студенту-локомотивщику | 0 | 24.02.2013 19:28 |

| =Диплом= Устройство и ремонт электродвигателя НБ-418 | Admin | Студенту-локомотивщику | 0 | 23.02.2013 08:57 |

| Ответить в этой теме |

| Возможно вас заинтересует информация по следующим меткам (темам): |

| , , , |

| Здесь присутствуют: 1 (пользователей: 0 , гостей: 1) | |

|

|