|

|

|

|

#1 (ссылка) |

|

Кандидат в V.I.P.

Регистрация: 14.05.2015

Сообщений: 193

Поблагодарил: 0 раз(а)

Поблагодарили 10 раз(а)

Фотоальбомы:

не добавлял

Репутация: 0

|

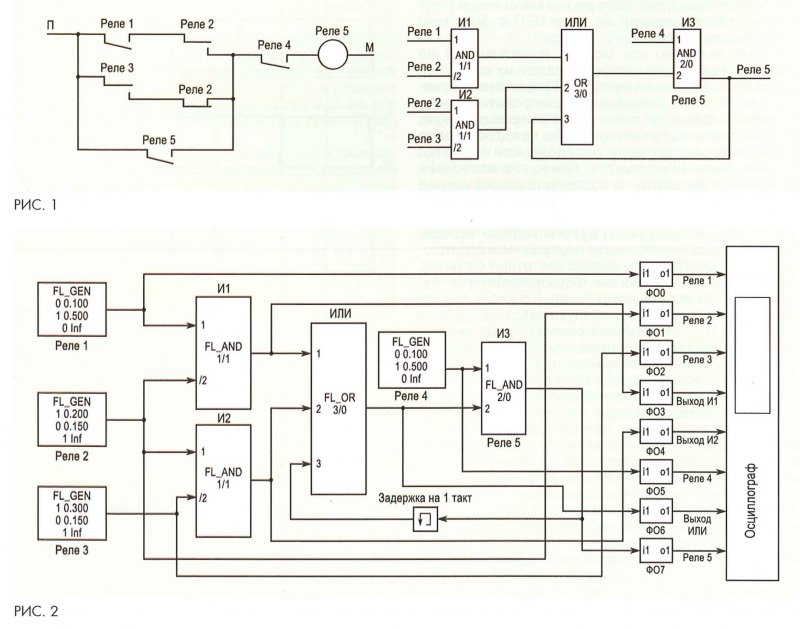

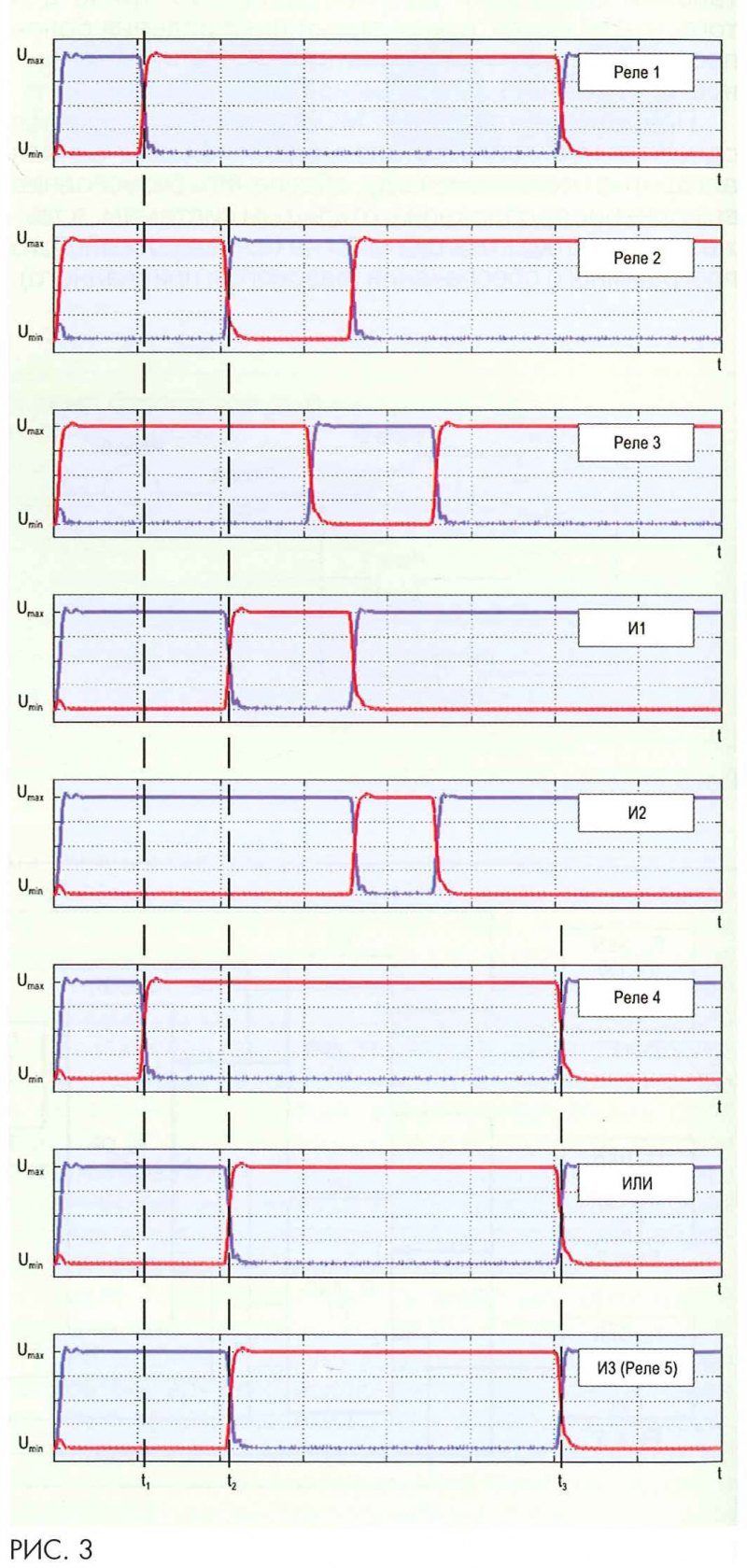

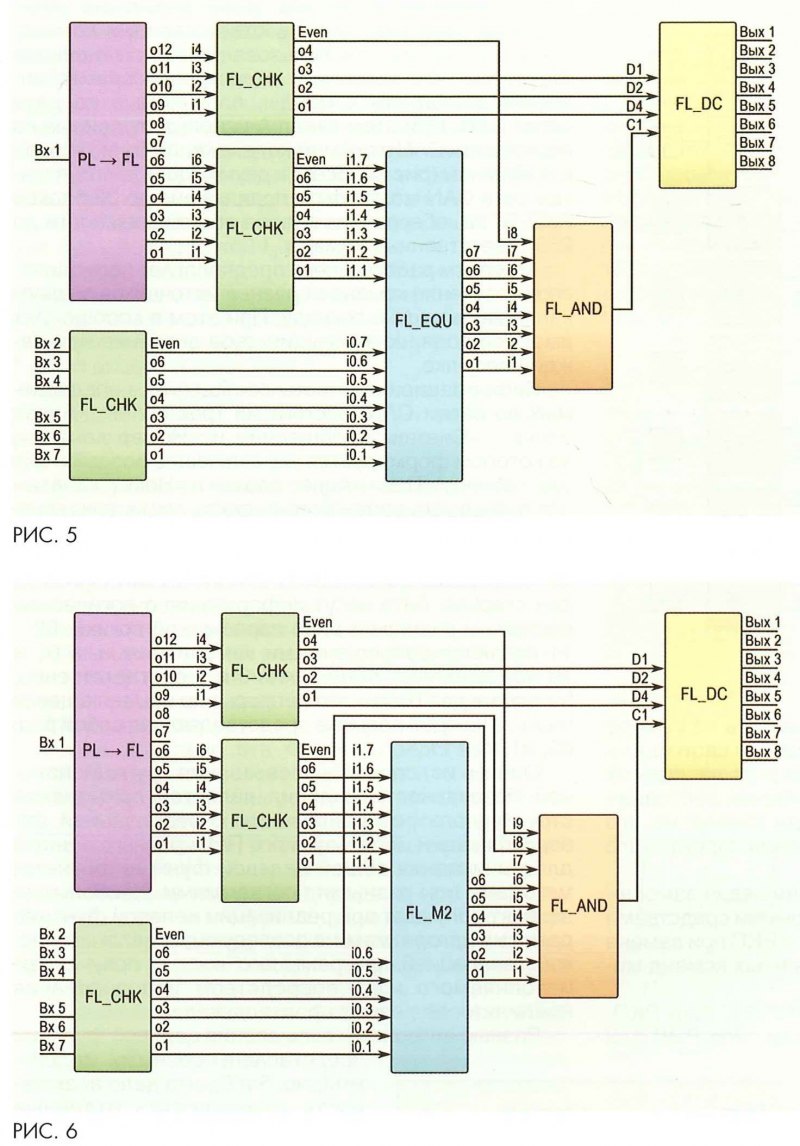

Тема: [02-2015] Модельно-ориентированное проектирование систем ЖАТМодельно-ориентированное проектирование систем ЖАТ И.Д. ДОЛГИЙ, заведующий кафедрой «Автоматика и телемеханика на ж.д. транспорте» ФГБОУ ВПО РГУПС, д-р техн. наук, профессор А.Г. КУЛЬКИН, заведующий НИЛ СДКУ, канд. техн. наук Ю.Э. ПОНОМАРЕВ, старший научный сотрудник, канд. техн. наук С.А. КУЛЬКИН, научный сотрудник, канд. техн. наук Ключевые слова: модельно-ориентированное проектирование, безопасная радиочастотная логика, базовый элемент, синтез релейных схем, автоматическая генерация кода В настоящее время затраты на разработку прикладного программного обеспечения (ПО) критичных к безопасности программно-аппаратных комплексов (ПАК), к которым относятся все микропроцессорные системы железнодорожной автоматики и телемеханики, достигают 80-90% общей стоимости разработки. К тому же с течением времени их доля постоянно увеличивается. Как показывает опыт эксплуатации, до 95% отказных ситуаций связаны именно со сбоями в ПО. В связи с этим на фоне естественного повышения объема функциональных требований и степени ответственности таких систем вопросы обеспечения безопасности (надежности) ПО крайне актуальны. Высокая стоимость микропроцессорных систем ЖАТ негативно влияет на темпы их внедрения. Улучшить ситуацию поможет применение специализированных систем автоматического проектирования (САПР), способных по минимуму входной информации (например, однониточному плану станции, таблице враждебности маршрутов и др.) обеспечить кратчайшие сроки проектирования и высокое качество проектной документации. Функция автоматического формирования всей необходимой документации для заводов-изготовителей и таблиц для тестирования системы как на заводе, так и на объекте внедрения позволит существенно снизить расходы на проектирование таких систем. Из требований по кибербезопасности, а также открытости алгоритмов и исходных кодов программ вытекает необходимость передачи последних на хранение в уполномоченные центры, способные выполнить последующую модификацию алгоритмов и программ. Одна из проблем, возникающих при хранении, состоит в том, что представленные алгоритмы не всегда однозначно соответствуют рабочему коду программ даже в случае их получения с использованием различных систем автоматизации проектирования. Это создает дополнительные проблемы при переходе на отечественную элементную базу. В связи с чем предлагается хранить только алгоритмы, причем не как таковые, а алгоритмы в форме, обеспечивающей однозначную автоматическую генерацию исходного кода. Их следует представлять в виде действующих моделей, разработанных и функционирующих с применением хорошо зарекомендовавших себя систем моделирования. Представленные модели должны адекватно работать в полном соответствии с техническим заданием от момента задания входных тестовых последовательностей до последующей автоматической генерации исходных кодов. Такой подход называется модельно-ориентированным проектированием (МОП) и имеет ряд преимуществ. Он не требует кодирования исполняемой программы вручную, исключая тем самым негативное влияние так называемого человеческого фактора. Тестирование в реальном масштабе времени на более ранних этапах создания системы сокращает и удешевляет циклы проектирования, позволяет создавать более надежные системы управления с лучшими рабочими характеристиками. Кроме того, генерация исполняемого кода увеличивает производительность и снижает стоимость приложения. Требование «открытости» предполагает применение открытого модельно-ориентированного проектирования модулей, блоков и комплексов, из которых затем будут строиться (компоноваться) реальные объектно-ориентированные системы ЖАТ. При таком подходе тестирование, верификация и доказательство выполняются на моделях, а исходный код ПО автоматически генерируется сертифицированными и тщательно проверенными средствами проектирования для любого типа процессора - не только уже имеющегося, но и вновь разработанного. Открытыми должны быть не только модели, но и все инструментальные средства и документация. Это нужно для того, чтобы сделать жизненный цикл изделия более прозрачным и оптимизировать показатели экономичности, надежности, безопасности и защищенности. Применение открытого МОП позволяет добиться однозначного соответствия модели (формы записи алгоритма) исходному коду, обеспечить безусловное выполнение требований к открытым системам, а также создать открытые системы на основе российского программного обеспечения (базового и прикладного). Использование инструментальных средств МОП дает возможность реализовать модульное построение системы, функциональную расширяемость и мобильность при переносе ПО на другую аппаратную платформу, а также упростить передачу исходных кодов системного программного обеспечения. Немаловажное значение при модельно-ориентированном проектировании имеет элементная база для построения модели. В качестве таковой предлагается применять блоки специализированной логики, которые оперируют кодами, представляющими собой синусоидальные сигналы частотой f0 или fv и функционируют в соответствии с таблицами истинности [1]. В отличие от традиционной логики, которая не позволяет точно позиционировать отказ без дополнительных схемных доработок, синусоидальные сигналы не трансформируются друг в друга, а могут только смешиваться.  Использование таких кодов дает возможность логическим элементам контролировать наличие разрешенных сигналов на каждом входе, а также извещать о появлении запрещенных комбинаций и, при необходимости, блокировать их действие. К запрещенным комбинациям относится наложение частотных сигналов или их отсутствие (аналоги короткого замыкания или обрыва в цепи соответственно). Такое свойство позволяет обнаруживать отказы с точностью до блока. Для оценки возможности применения безопасной радиочастотной логики (БРЛ) и отработки методов модельно-ориентированного проектирования специалисты РГУПС разработали модели базовых элементов специализированной логики в среде MATLAB - Simulink, имеющие ряд особенностей: на входы элементов поступают коды синусоидальных сигналов частотой f0 или f.,; с целью увеличения скорости реализации и сокращения числа вычислительных операций элемент «НЕ» инкапсулирован в элементы «И» и «ИЛИ»; в базовых логических элементах могут иметься от 1 до 16 входов и один выход; входы нумеруются последовательно начиная с единицы и могут быть прямыми и инверсными, обозначаясь соответственно «1» или «/1» ... «п» или «/п»; выход, как и входы, также может быть как прямым, так и инверсным. В случае инверсии он отображается символом «о» (отрицание). В центре элемента указывается его тип (И - AND, ИЛИ - OR), а строкой ниже через косую черту - количество прямых и инверсных входов. Библиотека элементов БРЛ обеспечивает синтез релейных схем любой сложности. На рис. 1 приведен пример представления релейной схемы в виде модели, реализованной на базе БРЛ с функцией самоблокировки реле. Более детально эта модель представлена на рис. 2. Для имитации состояния реле и их контактов используются блоки генерации (БГ) частотных сигналов типа FL_GEN, способные формировать импульсы любой сложности, в том числе и периодические. Для имитации состояния контактов каждого из реле предусмотрены сигналы определенной частоты. Причем, если имитируется замкнутое состояние фронтового контакта, то соответствующий сигнал поступает на прямой вход логического элемента, а если тылового, - то на инверсный. Временные диаграммы работы модели отображаются на восьмиканальном виртуальном осциллографе (рис. 3). При этом вместо частотных сигналов используются их огибающие. Формирователи огибающих Ф01-Ф08 вычисляют уровень сигнала для каждой из присутствующих частот, которые изменяются от Umax до Umin. На осциллограммах представлены графики изменения амплитуды частотных сигналов, на которых синий цвет огибающей соответствует частоте f0, а красный - fv О наличии логической единицы в канале (фронтовой контакт замкнут, реле под током) свидетельствует импульс Umax частотой (красная огибающая) при минимальном уровне сигнала частотой f0, а о логическом нуле - противоположная ситуация. Отсутствие на осциллограмме импульсов обеих частот говорит об обрыве в цепи, а их наложение - о коротком замыкании.  Очевидно, что в соответствии со схемой Реле 5 сработает и встанет на самоблокировку только после создания цепи его питания. Рассмотрим, как это происходит при реализации безопасной радиочастотной логики. На осциллограмме представлены графики функционирования логических элементов. Чтобы сработал хотя бы один из элементов (И1 или И2), на прямом входе должен появиться импульс сигнала частотой fv а на инверсном - f0. Для элемента И1 такая ситуация складывается только в момент t2, когда Реле 2 обесточивается, о чем говорит переход красной огибающей на уровень Umin. Его тыловой контакт замыкается, о чем свидетельствует импульс синей огибающей при уже вставшем под ток в момент t1 Реле 1. Таким образом срабатывают оба входа И1 - и прямой (1), и инверсный (/2). Сигнал с выхода И1 попадает на прямой вход 1 элемента ИЛИ, который срабатывает (импульс красной огибающей) и посылает сигнал на вход 2 элемента ИЗ. К этому моменту Реле 4 уже под током с момента tr что создает условия для появления сигнала на выходе ИЗ (Реле 5 притянуло якорь и замкнуло свой фронтовой контакт). Этот сигнал подается на прямой вход 3 ИЛИ, что обеспечивает рабочее состояние элемента ИЗ до момента t3, когда сигнал на его входе 1 пропадет из-за размыкания фронтового контакта Реле 4.  Впервые методы МОП в решении задач замещения релейных схем микропроцессорными средствами были применены в системе ДЦ-ЮГ с РКП при замене релейного дешифратора ответственных команд микропроцессорным [2].  Разработанный специалистами РГУПС блок РКП-БТУ8, размещенный в корпусе реле типа РЭЛ или Н1 и заменяющий восемь малогабаритных реле, способен выдавать восемь ответственных команд. Он спроектирован с использованием двухканальной структуры, что позволяет двум процессорам асинхронно выполнять команды, получаемые из двух сетей CAN. При этом канал А использует данные из первой сети CAN в прямом коде, а канал Б - из второй в инверсном (рис. 4). Всего к двум отдельным сегментам сети CAN может быть подключено до 32 блоков РКП-БТУ8, обеспечивающих в общей сложности до 256 ответственных команд. Алгоритм работы блока предполагает периодическое получение команд от разных источников по двум каналам дважды в секунду. При этом в сообщениях имеются поля, изменяющие свое значение при каждой посылке. Информационная часть сообщений, передаваемых по сетям CAN, состоит из трех полей: «Адрес блока», «Счетчик сообщений» и «Номер канала», на котором формируется управляющее воздействие (см. таблицу). Поля «Адрес блока» и «Номер канала» для повышения помехоустойчивости защищены контрольными разрядами - битами «четности». Каждый информационный разряд кодируется четырьмя битами-так называемой многозначной логикой. При этом два старших бита несут информацию о логическом состоянии разряда в виде парафазной логики: 00 и 11 являются запрещенными комбинациями, а 01 и 10 представляют логический 0 и 1 соответственно. Младшие два бита - это непрерывно изменяющаяся часть, в каждой посылке представляющая собой ряд: 00, 01,10 и 11. Одним из способов повышения функциональной безопасности изделия является применение структурного резервирования с реализацией диверсификации используемого ПО в разных каналах для вычисления общей целевой функции разными методами или разными программами. Наибольший эффект получают при реализации целевой функции разными алгоритмами с последующей автоматической генерацией программного кода и получением исполняемого кода посредством использования компиляторов разных производителей. Разные алгоритмы вычисления целевой функции представлены разными моделями (рис. 5 и 6), что дало возможность генерировать отличные друг от друга исходные коды для каналов А и В. Тем самым обеспечивается реализация одной и той же целевой функции с последующим асинхронным сравнением полученных результатов по схеме «И». Диверсификация ПО позволяет практически полностью исключить одновременный отказ в обоих вычислительных каналах при возникновении различных сбоев. Дополнительно к базовым элементам БРЛ были разработаны элементы, упрощающие реализацию моделей и ускоряющие вычисление конечной функции.  Элемент PL->FL преобразует сообщения, полученные по сети CAN в формате многозначной логики, в радиочастотные сигналы. Он контролирует изменения входных сообщений и прекращает выдачу сигналов на выходе при отсутствии изменений. Элемент FL_CHK работает в двух режимах, проверяя на четность или нечетность входные сигналы. Так, например, при проверке на четность кодовой комбинации D5-f.p D4-f0, D3-f0, D2-f.,, D1-f0 и DO-f0 формируется выходная частота f1, поскольку присутствует четное количество частот (две). При нечетном количестве входных частот f1 элемент формирует выходной сигнал с частотой f0. Аналогично выполняется проверка на нечетность (при четном количестве входных частот f1 на выходе будет формироваться частота f0, а при нечетном - f.,). Элемент FL_DC дешифрирует входные сигналы D2-D0 при наличии на управляющем входе сигнала с частотой fr При этом на одном из выходов, определяемых кодом сигналов D2-D0, появляется сигнал с частотой iv на всех остальных - f0. Так, например, при кодовой комбинации 02-^, D1-f0 и DO—f0, что соответствует в двоичном коде 1002 = 41(?, сигнал f1 появится на выходе 4. Элементы FL_EQU и FL_M2 выполняют функцию сравнения сигналов на одноименных входах. При наличии на них разных или одинаковых сигналов на выходе элемента FL_EQU будут генерироваться сигналы с частотой f0 или f1 соответственно. По аналогии с релейными системами элемент FL_M2 обеспечивает попарное сравнение входных сигналов и формирует сигнал частотой f0, если на одноименных входах будут одинаковые сигналы, или сигнал с частотой в противном случае. Указанные элементы выполняют те же функции, что и традиционная ТТЛ логика. Разница заключается в том, что используются другие входные и выходные сигналы. Наличие библиотеки базовых элементов БРЛ и их производных позволило разработать ПО блока РКП-БТУ8, проверить его функционирование и всесторонне протестировать работу на модели изделия до его аппаратной реализации. Автоматическая генерация кода для создания читабельного, эффективного, надежного и широко распространенного языка программирования (С-кода) промышленного качества из оттестированных моделей позволяет сократить время и стоимость разработки, улучшить качество и создать системы с более высокими эксплуатационными характеристиками. Программно-аппаратные средства, реализующие БРЛ, при надлежащей структурной организации могут заменить реле в ответственных схемах, обеспечить необходимый уровень функциональной безопасности, снизить массогабаритные размеры, повысить энергоэффективность и обеспечить открытость алгоритмов функционирования. ЛИТЕРАТУРА 1. Долгий И.Д., Кулькин А.Г., Кулькин С.А., Пономарев Ю.Э., Розенберг И.Н. Введение в безопасную радиочастотную логику // Известия ЮФУ. Технические науки, 2014 г., № 6, с. 229-238. 2. Долгий И.Д., Кулькин А.Г., Скопин А.А. Реализация ответственных команд в системе ДЦ-ЮГ с РКП //Автоматика, связь, информатика. 2003 г., № 2, с. 9-13. |

|

|

Цитировать 0 |

|

|

#2 (ссылка) |

|

Робот

Регистрация: 05.05.2009

Сообщений: 1,751

Поблагодарил: 0 раз(а)

Поблагодарили 82 раз(а)

Фотоальбомы:

не добавлял

Репутация: 0

|

Тема: Тема перенесена |

|

|

Цитировать 0 |

|

|

||||

| Тема | Автор | Раздел | Ответов | Последнее сообщение |

| =Приказ= № 513А от 27 апреля 2015 г. - О звуковом сигнале большой мощности 9 мая 2015 г. в 12-00 | Admin | Документы Дирекции тяги ОАО "РЖД" | 0 | 01.05.2015 14:51 |

| Проектирование систем энергоснабжения электрических железных дорог (Бесков Б.А., Геронимус Б.Е. и др.) | Admin | Библиотека | 0 | 13.12.2014 05:59 |

| Проектирование систем СЦБ | ШНС СЦБ | Схемная группа | 1 | 13.07.2012 12:42 |

| Проектирование новых систем | Андрей13 | Общие вопросы эксплуатации устройств СЦБ | 9 | 25.12.2009 03:38 |

| =Курсовая работа= Проектирование канала низкой частоты и каналообразующего оборудования многоканальных систем связи | СЦБист | Дипломы, курсовые, лекции, рефераты по СЦБ | 0 | 15.08.2009 06:55 |

| Ответить в этой теме Перейти в раздел этой темы Translate to English |

| Возможно вас заинтересует информация по следующим меткам (темам): |

| , , , , |

| Здесь присутствуют: 1 (пользователей: 0 , гостей: 1) | |

|

|