МИНИСТЕРСТВО ПУТЕЙ СООБЩЕНИЯ

РОССИЙСКОЙ ФЕДЕРАЦИИ

РТМ 32 ЦШ 1115842.01—94

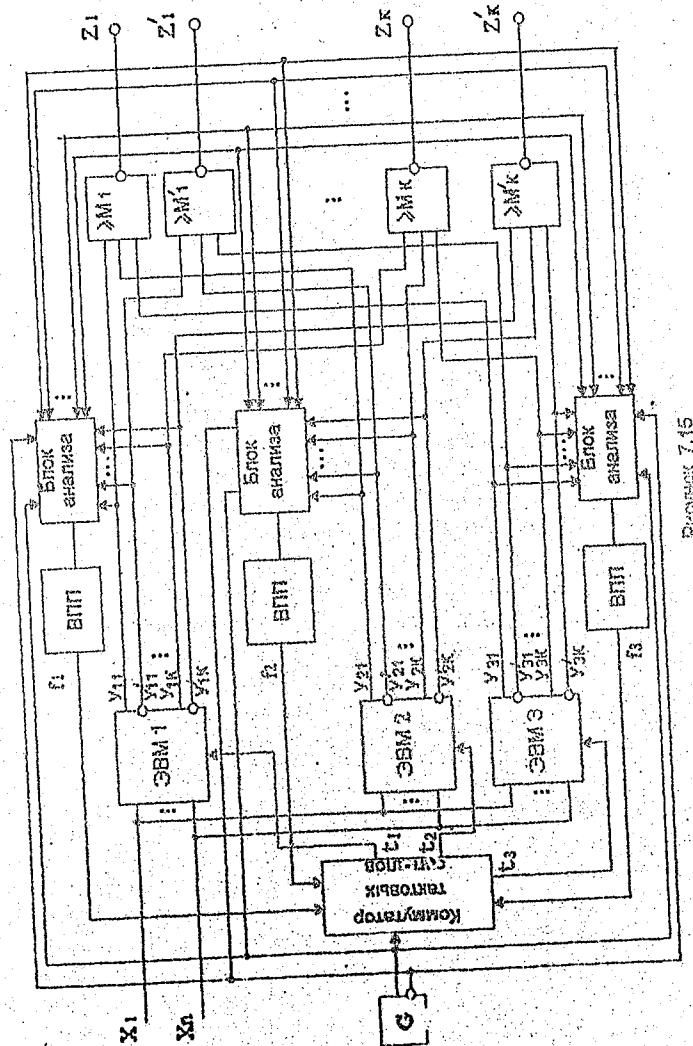

РУКОВОДЯЩИЙ ТЕХНИЧЕСКИЙ МАТЕРИАЛ

БЕЗОПАСНОСТЬ ЖЕЛЕЗНОДОРОЖНОЙ

АВТОМАТИКИ И ТЕЛЕМЕХАНИКИ

Методы и принципы обеспечения безопасности

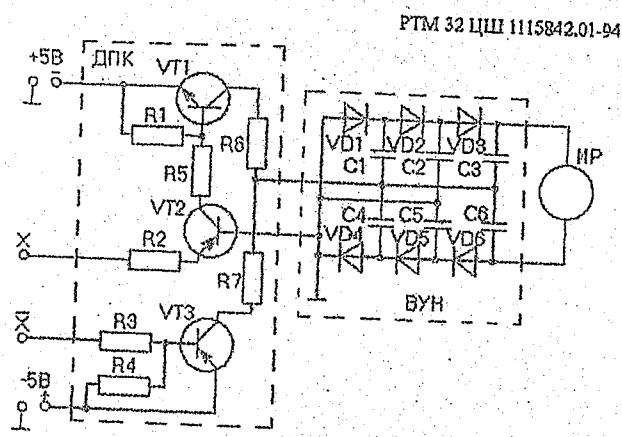

микроэлектронных СЖАТ

Издание официальное

САНКТ-ПЕТЕРБУРГ

1994

ledyaev@test-center.spb.ru

29.08.2017 12:58

ПРЕДИСЛОВИЕ

1 РАЗРАБОТАН И ВНЕСЕН Управлением сигнализации, связи и вычислительной техники МПС, Петербургским государственным университетом путей сообщения

РАЗРАБОТЧИКИ: Вл. В. Сапожников, академик АТ РФ, д-р техн. наук (руководитель), В. В. Сапожников, академик АТ РФ, д-р техн. наук, Д. В. Гавзов, канд. техн. наук (ответственный исполнитель), В. И. Талалаев, О. А. Наседкин, канд. техн. наук, М. В. Илюхин, Д. М. Котельников

2 УТВЕРЖДЕН начальником Управления сигнализации, связи и вычислительной техники МПС РФ Г. Ф. Лекутой 10 февраля 1994 г.

3 ВВЕДЕН ВПЕРВЫЕ

СОДЕРЖАНИЕ

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| ОВЛАСТЬ ПРИМЕНЕНИЯ.....                                                                        | 1  |

| НОРМАТИВНЫЕ ССЫЛКИ.....                                                                        | 2  |

| 1 МЕТОДЫ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ И БЕЗОТКАЗНОСТИ МИКРОЭЛЕКТРОННЫХ СХЕМ.....                   | -  |

| 2 СТРУКТУРНЫЕ МЕТОДЫ ПОВЫШЕНИЯ НАДЕЖНОСТИ СХЕМ.....                                            | 10 |

| 2.1 Анализ резервированных структур .....                                                      | -  |

| 2.2 Применение мажоритарного резервирования для повышения показателей надежности МЭС.....      | 14 |

| 3 СТРУКТУРЫ БЕЗОПАСНЫХ МИКРОЭЛЕКТРОННЫХ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ.....                        | 17 |

| 3.1 Структуры безопасных микропроцессорных модулей.....                                        | 18 |

| 3.2 Аппаратный контроль и способы локализации отказов микропроцессорных систем автоматики..... | 23 |

| 4 ПРИНЦИПЫ ПОСТРОЕНИЯ БЕЗОПАСНЫХ СХЕМ НА ЭЛЕМЕНТАХ С НЕСИММЕТРИЧНЫМИ ОТКАЗАМИ.....             | 33 |

| 4.1 Элементы с несимметричными отказами.....                                                   | -  |

| 4.2 Принципы построения безопасных комбинационных схем.....                                    | -  |

| 4.3 Функциональная полнота безопасных элементов.....                                           | 38 |

| 4.4 Принципы построения безопасных схем с памятью на безопасных элементах.....                 | 40 |

| 5 ИСПОЛЬЗОВАНИЕ САМОПРОВЕРЯЕМЫХ СХЕМ ПРИ ПОСТРОЕНИИ БЕЗОПАСНЫХ СИСТЕМ.....                     | 45 |

| 5.1 Структура самопроверяемого дискретного устройства.....                                     | -  |

| 5.2 Принципы использования самопроверяемых ДУ в безопасных системах.....                       | -  |

| 5.3 Принципы контроля ДУ.....                                                                  | -  |

| 5.4 ДУ с контролем по внутреннему состоянию.....                                               | 47 |

| 5.5 ДУ с контролем по выходному состоянию.....                                                 | -  |

| 5.8 Самопроверяемое ДУ со свойством блокировки.....                                            | 49 |

| 5.7 Определение самопроверяемого ДУ.....                                                       | -  |

| 5.8 Самопроверяемые тестеры.....                                                               | 50 |

| 5.9 Способ описания тестеров.....                                                              | 51 |

| 5.10 Каталог тестеров для равновесных кодов.....                                               | -  |

## РУКОВОДЯЩИЙ ТЕХНИЧЕСКИЙ МАТЕРИАЛ

Методы и принципы обеспечения безопасности

микроэлектронных СЖАТ

Дата введение 1994-06-01

## ОБЛАСТЬ ПРИМЕНЕНИЯ

Настоящий руководящий технический материал рассчитан на работников научно-исследовательских, проектно-конструкторских и испытательных организаций. Он распространяется на дискретные устройства, системы железнодорожной автоматики и телемеханики (СЖАТ), а также определяет основные правила и методы обеспечения безопасности микроэлектронных схем. В данном документе под микроэлектронными схемами подразумеваются схемы, построенные на электронных элементах, микросхемах, микропроцессорах и микроЭВМ.

Требования настоящего руководящего технического материала должны использоваться разработчиками с учетом специфики области применения конкретных устройств (например для обработки аналоговых сигналов и т.д.).

Данный руководящий документ является открытым для дополнений и изменений, связанных со спецификой устройств и с расширением области его распространения, а также с появлением новых технических решений, элементов и совершенствованием известных схем, отвечающих требованиям безопасности.

Все дополнения и изменения осуществляются установленным для нормативных документов порядком.

Использование данного документа не отменяет общего порядка проведения испытаний на безопасность в соответствии с ОСТ 32.19, РД ПШ 1115842.01-93 и РД 32 ПШ 1115842.02-93.

Термины и определения, используемые в данном документе, соответствуют ОСТ 32.17 и ГОСТ 27.002.

|                                                                                             |           |

|---------------------------------------------------------------------------------------------|-----------|

| РТМ 32 ПШ 1115842.01-94                                                                     |           |

| 5.11 1/3-СИТ.....                                                                           | 54        |

| 6.12 Самопроверяемый фиксатор ошибок.....                                                   |           |

| 6.13 Внутренняя структура самопроверяемого ДУ.....                                          | 67        |

| 5.14 Стратегии поведения самопроверяемых дискретных систем.....                             | 61        |

| <b>6 ПРОГРАММНЫЕ МЕТОДЫ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ СИСТЕМ ЖЕЛЕЗНОДОРОЖНОЙ АВТОМАТИКИ.....</b> | <b>64</b> |

| 6.1 Методы обеспечения надежности программных средств.....                                  |           |

| 6.2 Специфика программного обеспечения как средства контроля.....                           | 70        |

| 6.3 Основные понятия и критерий оценки методов контроля.....                                | 71        |

| 6.4 Программные методы обеспечения безопасности.....                                        | 74        |

| <b>7 БЕЗОПАСНЫЙ ИНТЕРФЕЙС.....</b>                                                          | <b>79</b> |

| 7.1 Требования к специализированным УСО.....                                                | 80        |

| 7.2 Классификация элементов сопряжения.....                                                 | 82        |

| 7.3 Устройства включения исполнительных реле.....                                           | 84        |

| 7.4 Бесконтактные УСО.....                                                                  | 90        |

| 7.5 Безопасный ввод информации.....                                                         | 97        |

| <b>8 БЕЗОПАСНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ.....</b>                                                | <b>99</b> |

| Приложение А. Библиография.....                                                             | 108       |

| Список использованной литературы к разделу 1.....                                           |           |

| Список использованной литературы к разделу 2.....                                           | 109       |

| Список использованной литературы к разделу 3.....                                           | 110       |

| Список рекомендуемой литературы к разделу 4.....                                            | 112       |

| Список рекомендуемой литературы к разделу 5.....                                            |           |

| Список использованной литературы к разделу 6.....                                           | 114       |

| Список использованной литературы к разделу 7.....                                           |           |

| Список использованной литературы к разделу 8.....                                           | 116       |

## НОРМАТИВНЫЕ ССЫЛКИ

В настоящем руководящем техническом материале использованы ссылки на следующие стандарты:

- ГОСТ 27.002-83. Надежность в технике. Термины и определения;

- ОСТ 32.17-92. Безопасность железнодорожной автоматики и телемеханики. Основные понятия. Термины и определения;

- ОСТ 32.19-92. Безопасность железнодорожной автоматики и телемеханики. Общие требования к программам обеспечения безопасности.

### 1 МЕТОДЫ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ И БЕЗОТКАЗНОСТИ МИКРОЭЛЕКТРОННЫХ СКАТ

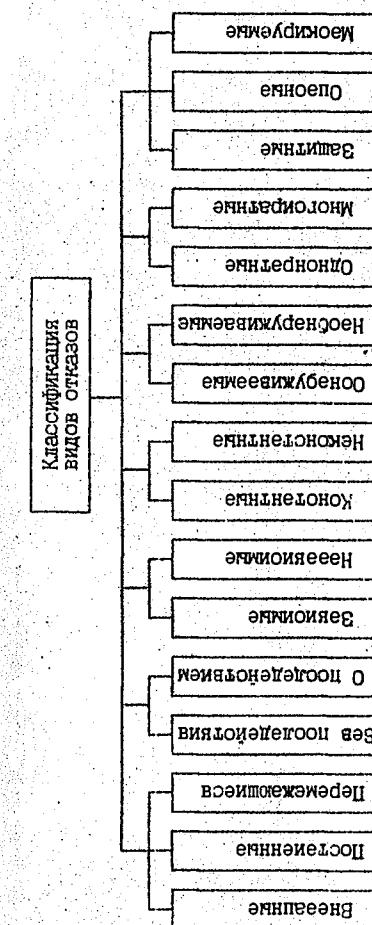

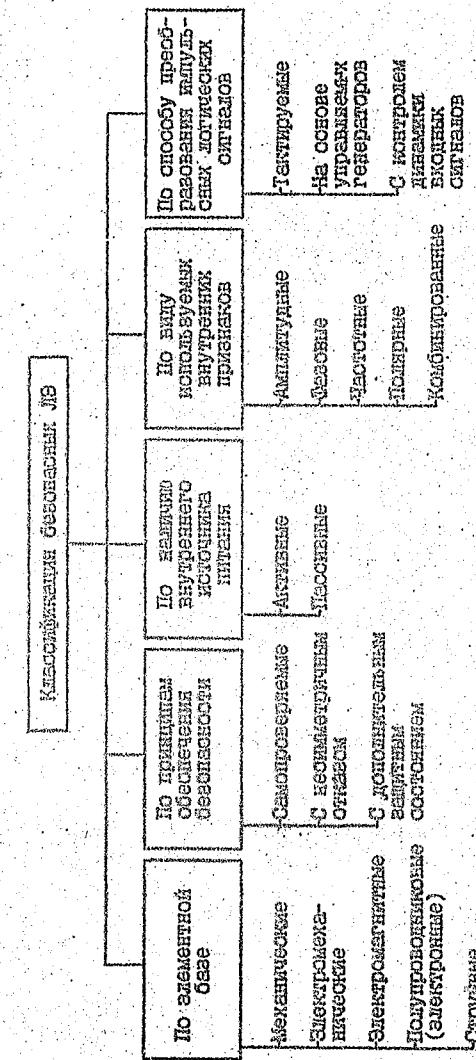

Выбор методов достижения требуемых показателей безотказности и безопасности осуществляется на основе анализа возможных отказов (рисунок 1.1) элементов СКАТ [1.1], [1.2].

В релейных системах железнодорожной автоматики отказы разделяются на защитные и опасные. Появление сложных микроэлектронных элементов привело к выделению нового класса отказов - маскируемых.

Дефекты технических средств, которые не приводят к нарушению функционирования системы, называются маскируемыми и могут быть обнаруживаемыми и необнаруживаемыми. Последние могут приводить к накоплению неисправностей и, как следствие, к возможности появления опасных отказов.

В отличие от релейных СКАТ проблема безотказности и безопасности комплексно может быть решена не за счет применения более надежных элементов, а за счет использования различных методов реагирования и контроля.

Это в значительно большей степени относится к безопасности, которая обеспечивается определенным комплексом мероприятий, устанавливаемых концепцией безопасности.

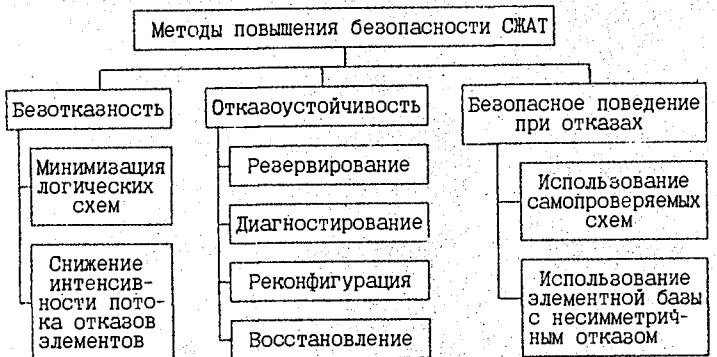

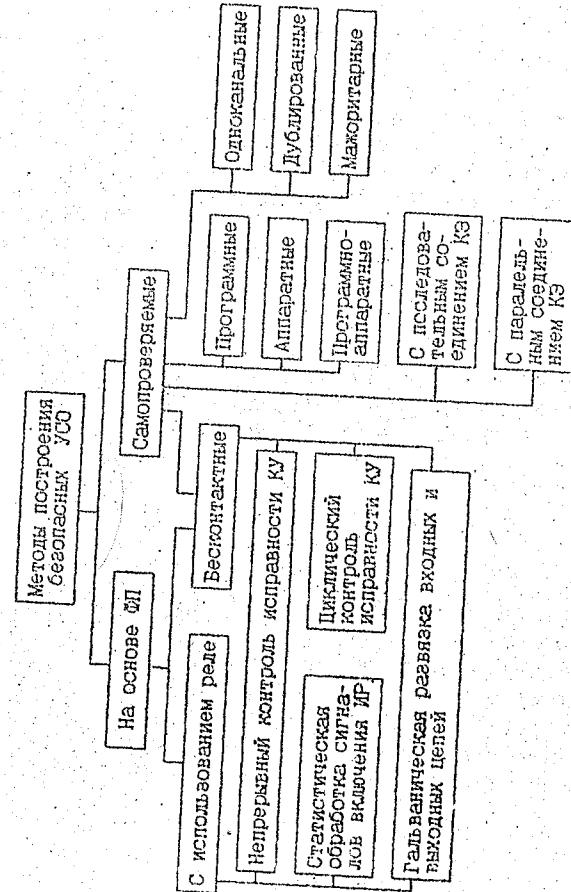

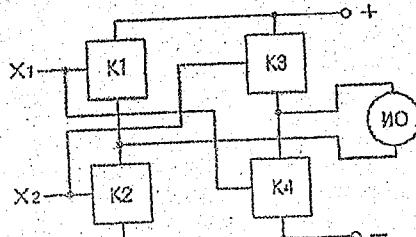

Для реализации концепций безопасности микроэлектронных СКАТ используются три стратегии (рисунок 1.2): безотказность

Рисунок 1.1

Рисунок 1.2

4

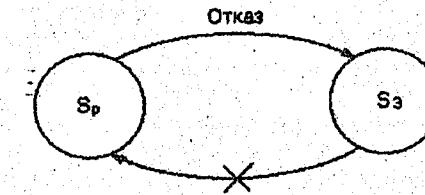

(reliability), отказоустойчивость (fault-tolerance) и безопасное поведение при отказах (fail-safe) [1.1], [1.9], [1.11], [1.13]. Первые две стратегии подразумевают, что система, которая правильно выполняет свой алгоритм функционирования, безопасна. Третья стратегия используется специально для безопасных систем и заключается в переводе системы в защитное необратимое состояние при появлении отказа (рисунок 1.3). Обратный переход в работоспособное состояние исключается (маловероятен) и производится искусственным путем (обычно с участием человека).

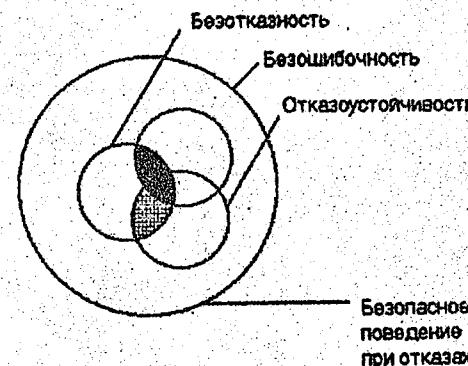

Графическая интерпретация взаимодействия этих стратегий между собой при построении безопасных систем отображена на рисунке 1.4. Безопасность технических средств в значительной степени определяется влиянием человеческого фактора на всех стадиях жизненного цикла (разработки, изготовления и эксплуатации). Поэтому для создания безопасных технических средств должна дополнительно использоваться стратегия безошибочности.

С широким внедрением полупроводниковых и микроэлектронных элементов появилась необходимость в разработке и исследовании дополнительных мер по защите от опасных отказов устройств, выполненных на их основе [1.2], [1.6]-[1.9].

Первоначально в электронных системах автоматики [1.10]-[1.13] необходимый уровень безопасности достигался за счет выполнения их на элементах с несимметричным отказом, не требующих специальных мер защиты от опасных отказов, - на электронных аналогах реле 1 класса надежности.

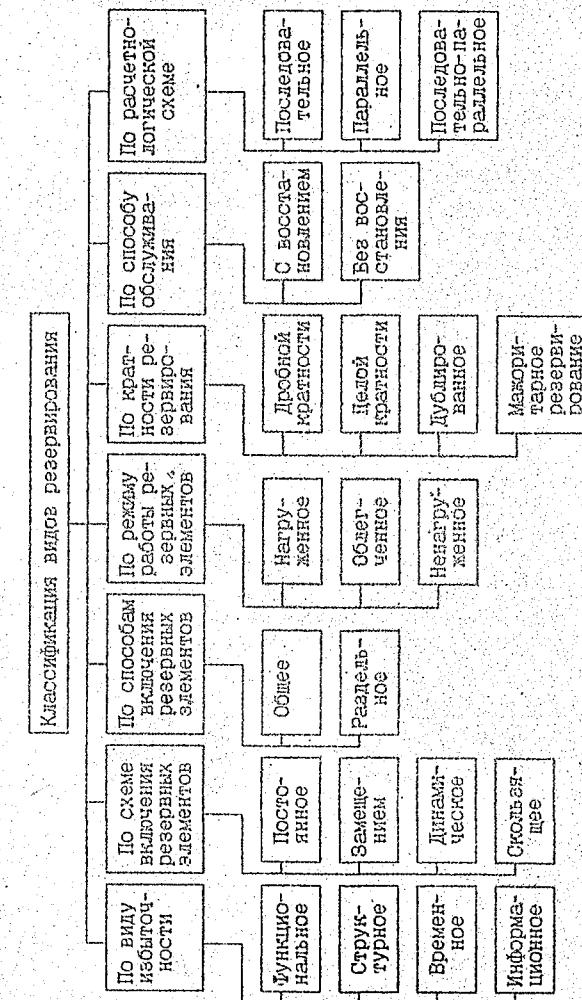

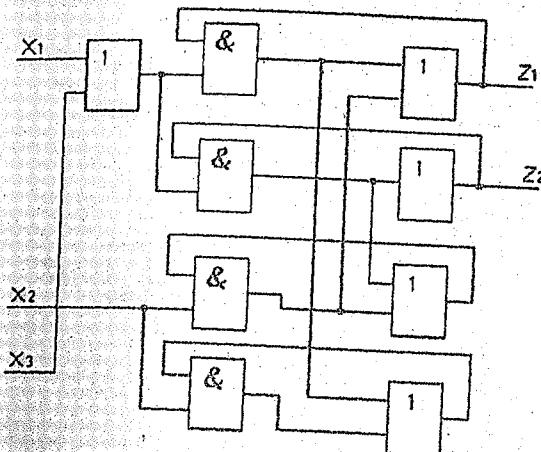

Более перспективным является реализация сложных СЖАТ на интегральных микросхемах большой степени интеграции (БИС). При использовании такой элементной базы для достижения необходимых показателей безопасности применяют сочетание различных видов резервирования (рисунок 1.5) с контролем и диагностикой появления сбоев и отказов элементов. Контроль осуществляется устройством с несимметричной характеристикой отказов.

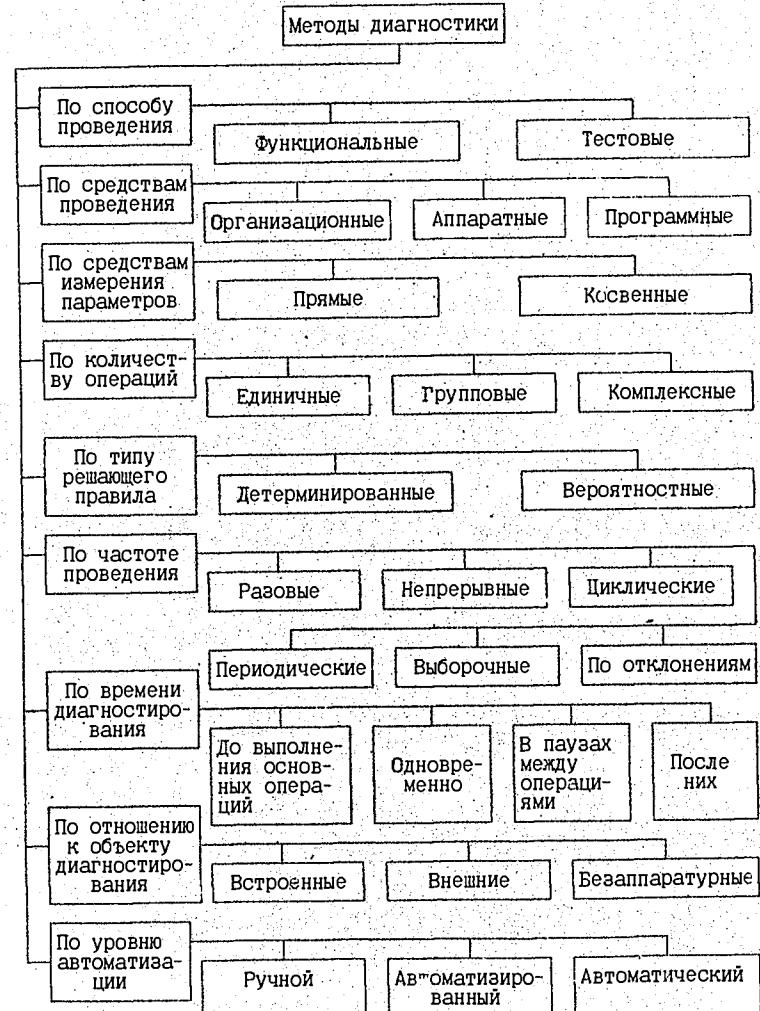

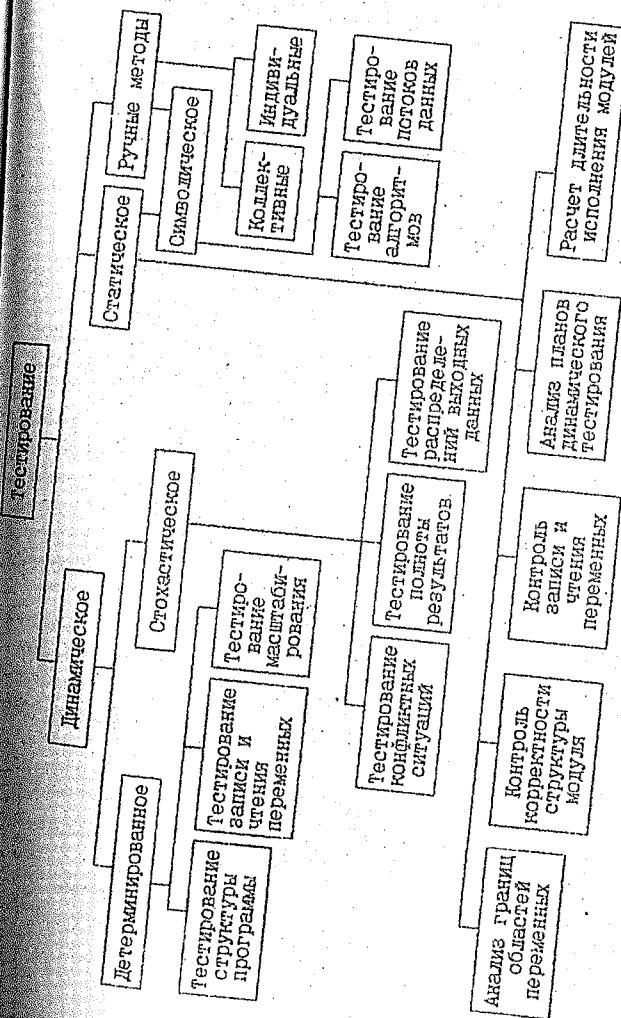

Классификации методов диагностики приведена на рисунке 1.6.

При разработке СЖАТ на основе микроэлектронных элементов большой степени интеграции (например микропроцессоров) необходимо учитывать, что многие их элементы используются многократно в

Рисунок 3

Рисунок 1.4

Рисунок 1.5

ходе выполнения программы. Кроме того, отдельные отказы БИС могут быть многократными. Например, отказы в питающих выводах приводят к искажениям в работе многих элементов БИС, к появлению новых связей и элементов (паразитных элементов). Последствия этого могут проявляться в различных частях БИС, даже косвенно связанных с первоначальными обстоятельствами.

Поэтому при синтезе СЖАТ на основе микропроцессоров (МП) необходимо считаться с многократными отказами. Современные МП характеризуются высокой степенью интеграции и малым числом выводов, поэтому их полная проверка требует значительного времени и практически невозможна.

Необходимые показатели безотказности, контролепригодности и безопасности микропроцессорных систем автоматики достигаются за счет использования структурного резервирования, которое можно подразделить на аппаратное и программное, т.е. используется способ параллельной обработки информации в нескольких микроЭВМ или с помощью нескольких программ в одной микроЭВМ.

Для контроля правильности работы каналов обработки информации используется аппаратное или программное сравнение результатов выполнения отдельных команд или решения отдельных задач.

Используемые методы резервирования и контроля в СЖАТ, отвечающие требованиям безопасности, должны обеспечивать:

- независимость отказов в однотипных элементах функционально избыточных структур;

- защиту системы от сбоев и отказов, исключение возможности накопления отказов;

- контроль правильности функционирования программного обеспечения.

При структурном резервировании критическими узлами с точки зрения независимости отказов в различных вычислительных каналах являются входная и выходная информация, питание, достоверность работы устройств контроля, однотипные ошибки программного обеспечения.

Для защиты от искажений входную информацию вводят в МП СЖАТ в виде последовательного избыточного кода или по нескольким параллельным гальванически разведенными цепям. Питание различных

микроЭВМ должно быть автономным, а управляющие воздействия на исполнительные органы осуществляться по методу накопления выходных сигналов, т.е. по интегральной оценке избыточной информации, что позволит также обеспечить необходимый уровень помехоустойчивости СЖАТ [1.12].

Программные методы резервирования и контроля требуют большего, чем аппаратные, времени обнаружения отказов, и при их использовании трудно обеспечить требование независимости отказов в различных программах обработки информации [1.13].

Для обеспечения независимости отказов программных модулей создаются разные коллективы программистов, используются инверсные данные и т.п. Все эти меры приводят к увеличению стоимости разработки МП СЖАТ, т.к. затраты на создание программного обеспечения достигают 70% [1.14]. Кроме того, в настоящее время не существует теоретического подтверждения обеспечения безопасности МП-средств, использующих только программные методы резервирования и контроля. Таким образом, в МП СЖАТ для обеспечения безопасности необходимо использовать сочетание программных и аппаратных методов [1.1], [1.2].

## 2 СТРУКТУРНЫЕ МЕТОДЫ ПОВЫШЕНИЯ НАДЕЖНОСТИ СЖАТ

### 2.1 Анализ резервированных структур

В большинстве существующих микроэлектронных систем (МЭС), отвечающих за безопасность, используются аппаратные методы резервирования и контроля [2.13]-[2.4].

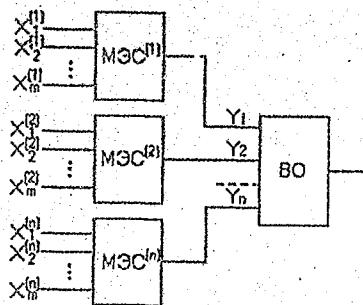

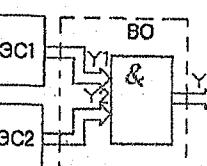

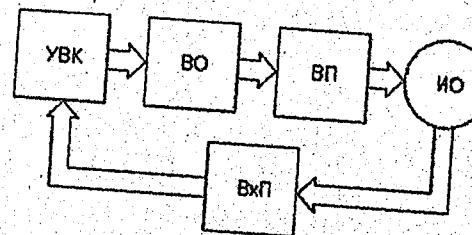

В общем виде резервированная структура МЭС приведена на рисунке 2.1. Резервироваться может как все устройство, так и его отдельные узлы.

Величина  $n$ , называемая кратностью резервирования, характеризует число идентичных каналов или элементов, обеспечивающих соответственно получение или обработку информации.

Неотъемлемой частью избыточных устройств являются восстанавливающие органы (ВО), осуществляющие коррекцию ошибок, возникающих при сбоях и отказах аппаратуры, и реализующие в большинстве случаев пороговую функцию.

Рисунок 2.1

$$Y = M_2^1 = Y_1 \vee Y_2$$

$$Y = M_2^2 = Y_1 \cdot Y_2$$

Рисунок 2.2

Рисунок 2.3

$$Y = M_3^1 = Y_1 \vee Y_2 \vee Y_3 \vee \bar{Y}_1 \vee \bar{Y}_2 \vee \bar{Y}_3$$

Рисунок 2.4

При неисправности какого-либо из обрабатывающих каналов МЭС на его выходе может появиться ложная 1 или ложный 0. Правильный сигнал на выходе избыточной структуры появляется только при определенном числе ложных сигналов 0 и 1 на выходах  $Y_i$  МЭС.

Естественно, чем выше кратность резервирования  $n$ , тем больше ошибок на выходах логических блоков будет корректироваться.

В общем виде пороговая функция ВО с равными весами может быть записана [2.5]:

$$y = M_n^P - f(y_1, y_2, \dots, y_n) = \begin{cases} 1, & \text{если } \sum_{i=1}^n y_i - p > 0 \\ 0, & \text{если } \sum_{i=1}^n y_i - p < 0, \end{cases} \quad (2.1)$$

где  $p$  - порог восстанавливающего органа.

В таблице 2.1 указано количество ошибок, исправляемых ВО с различными пороговыми функциями  $y = M_n^P$ .

Таблица 2.1

| Кратность<br>резервирования<br>$n$ | Функция<br>ВО                 | Количество корректируемых ошибок |             |

|------------------------------------|-------------------------------|----------------------------------|-------------|

|                                    |                               | Ложный 0                         | Ложная 1    |

| 1                                  | 2                             | 3                                | 4           |

| 1                                  | $M_1^1$                       | 0                                | 1           |

| 2                                  | $M_2^1$<br>$M_2^2$            | 1<br>0                           | 0<br>1      |

| 3                                  | $M_3^1$<br>$M_3^2$<br>$M_3^3$ | 2<br>1<br>0                      | 0<br>1<br>2 |

| 4                                  | $M_4^1$<br>$M_4^2$<br>$M_4^3$ | 3<br>2<br>1                      | 0<br>1<br>2 |

| 1   | 2                                                   | 3                     | 4                     |

|-----|-----------------------------------------------------|-----------------------|-----------------------|

|     | $M_4^4$                                             | 0                     | 3                     |

| 5   | $M_5^1$<br>$M_5^2$<br>$M_5^3$<br>$M_5^4$<br>$M_5^5$ | 4<br>3<br>2<br>1<br>0 | 0<br>1<br>2<br>3<br>4 |

| $n$ | $M_n^P$                                             | $n-p$                 | $p-1$                 |

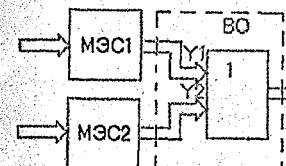

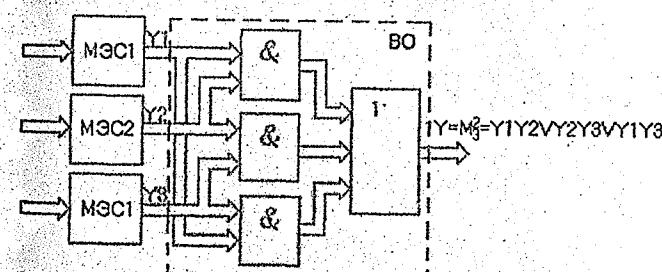

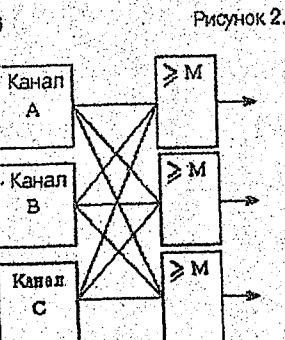

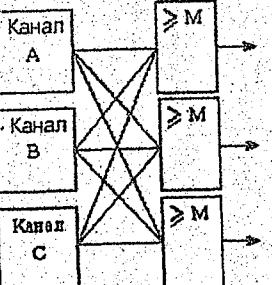

На рисунках 2.2-2.4 приведены примеры МЭС с ВО, реализующими функции  $M_1^1$ ,  $M_2^2$ ,  $M_3^2$ .

Из таблицы 2.1 видно, что симметричной способностью корректировать ошибки типа "ложный 0" и "ложная 1" обладают ВО, реализующие мажоритарную функцию  $M_3^2$ ,  $M_5^3$  и т. п.; ошибки типа "ложный 0" лучше всего исправляют ВО, реализующие функцию ИЛИ, а ошибки типа "ложная 1" - ВО, реализующие функцию И.

Таким образом, зная вероятности появления ложных сигналов 0, 1 и предпочтительное значение выходных сигналов, выбирают тип ВО. С точки зрения обеспечения безопасности наилучшим является ВО типа И, но по сравнению с неизбыточными такими МЭС обладают худшими показателями безотказности.

МЭС с мажоритарными ВО позволяют найти компромиссное решение для достижения необходимых показателей безотказности и безопасности.

Анализ различных видов структурного резервирования показывает, что всем им, кроме мажоритарного, присущи следующие недостатки: сложность коммутации и перерыв в работе системы по основной программе при замене отказавшего элемента или комплекта исправным.

Необходимо отметить, что мажоритарное резервирование позволяет защититься не только от постоянных отказов, но и от переме-

жающихся, в том числе и от воздействия помех, т.к. они обычно проявляются неодинаково в резервированных каналах обработки информации [2.6].

## 2.2 Применение мажоритарного резервирования для повышения показателей надежности МЭС

При мажоритарном резервировании организуется нечетное число каналов обработки информации МЭС, выходные сигналы которых объединяются с помощью восстанавливающего органа (мажоритарного элемента МЭ).

Сигнал на выходе МЭ определяется большинством ( $p > \frac{n+1}{2}$ ) входных сигналов. Отказ или сбой  $\frac{n-1}{2}$  каналов обработки информации не приводит к отказу системы в целом. Поэтому работоспособность отдельных каналов можно восстанавливать без прерывания работы системы, что позволяет значительно увеличить ее коэффициент готовности.

Низкая надежность отдельных блоков аппаратуры, а также значительное время восстановления неисправных узлов и элементов может быть скомпенсировано повышением кратности мажоритарного резервирования. Однако при обычном использовании таких резервированных устройств используются не все достоинства высокой кратности.

С увеличением кратности число резервируемых блоков  $n$  растет быстрее, чем величина  $K+1$  – число блоков, при выходе из строя которых вся резервируемая группа прекращает работу, а значит растет число исправных блоков, остающихся незадействованными после отказа мажоритарно-резервированной группы.

При изменении структуры мажоритарного элемента (снижении кратности резервирования) возможно использование оставшихся исправных блоков, т.е. можно увеличить время наработки на отказ всей резервированной группы. Например, при работе МЭ по принципу 3v5 отказ наступает при неисправной работе любых трех блоков, а два блока остаются работоспособными. Если в момент исправности трех блоков преобразовать схему МЭ 3v5 в 2v3, то работоспособность всей системы будет сохранена до тех пор, пока остаются исправными

два блока.

Такого рода преобразование может быть выполнено путем понижения порога в МЭ. В этом случае мажоритарность сохраняется до полного отказа; но он применим только при высокой кратности ( $n>3$ ) резервирования системы.

Возможно перестроение структуры с переходом к другому виду резервирования – дублированию. Этот способ является частным случаем адаптивных МЭ с цикловой адаптацией [2.7]. Если длительное время (несколько циклов) на одном из входов существовал ложный сигнал, то вес этого входа постепенно уменьшается до нуля, данный блок отключается от МЭ, а оставшиеся два переходят в режим работы по схеме И.

В этом случае общая надежность МЭ и его защищенность от появления ложного сигнала 1 на выходе повышается с сохранением общих параметров работоспособности. Это возможно либо подачей на отключаемый вход ВО логического 0 (в логических МЭ), либо снижением до нуля веса неисправного входа (для пороговых МЭ).

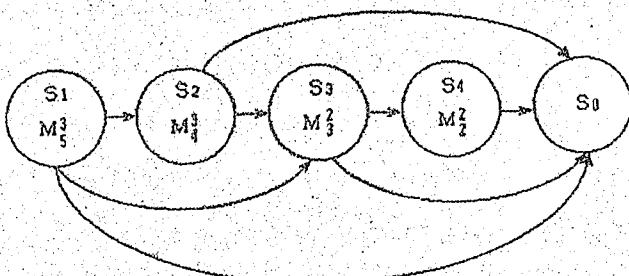

Граф возможных состояний адаптивной мажоритарно-резервированной системы (МРС) 3v5 приведен на рисунке 2.5. Средняя наработка на отказ такой адаптивной системы  $T_r = 1,28 T_0$  [2.7].

Таким образом, адаптивные мажоритарные системы позволяют значительно повысить показатели безотказности аппаратуры даже без восстановления отказавших каналов обработки информации.

Практическую реализацию адаптивных МЭ наиболее целесообразно выполнять программно, т.к. в аппаратном выполнении они получаются довольно сложными и, следовательно, имеют не очень высокие показатели безотказности, что соответственно снижает эффективность резервирования.

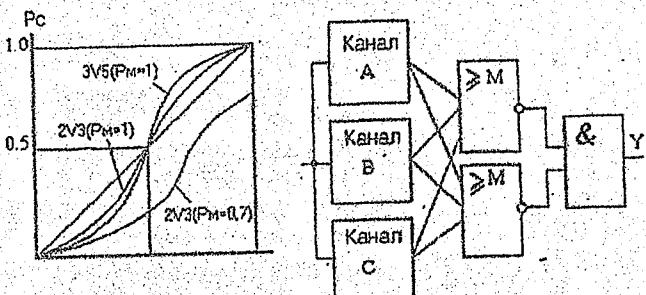

На рисунке 2.6 приведены зависимости вероятности безотказной работы МРС 2v3 и 3v5 (без восстановления) от вероятности безотказной работы резервируемого канала при  $R_m=\text{const}$ . Они имеют S-образный характер, и можно сделать вывод, что в избыточных структурах 2v3, 3v5 с однократной связью [2.5], [2.6] возможен выигрыш в надежности при наличии высоконадежного МЭ ( $R_m \rightarrow 1$ ), если вероятность безотказной работы неизбыточного канала обработки информации  $P_o > 0,5$ . Недостатком таких структур является то, что вероят-

Рисунок 2.5

Рисунок 2.6

Рисунок 2.7

Рисунок 2.8

нность их безотказной работы не превосходит вероятности безотказной работы МЭ и в случае отказа последнего отказывает вся избыточная структура.

С этой точки зрения еще более высокие требования предъявляются к надежности МЭ при дублировании его по схеме И (рисунок 2.7) [2.8].

Больший эффект от повышения надежности избыточной структуры МЭС можно получить, используя мажоритарное резервирование с многократными связями (рисунок 2.8) [2.6].

### 3 СТРУКТУРЫ БЕЗОПАСНЫХ МИКРОЭЛЕКТРОННЫХ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Безопасность функционирования МП-систем зависит в основном от интенсивности потока отказов элементов микроэВМ, длительности периода контроля МП-модуля ( $\tau_d$ ), закона формирования выходных воздействий системы (конъюнкции, пороговой или мажоритарной функции) и глубины (дискретизации) контроля.

Наиболее широко распространенная концепция безопасности микроЭлектронных СЖАТ требует, чтобы одиночные дефекты аппаратных и программных средств не приводили к опасным отказам и обнаруживались с заданной вероятностью на рабочих или тестовых воздействиях не позднее, чем в системе возникнет второй дефект. Проблема усложняется, если не все одиночные дефекты обнаруживаются. Тогда новый отказ может привести к нарушению безопасности. Поэтому необходимо предъявлять высокие требования по достоверности контроля программно-аппаратных средств и уменьшать время тестирования аппаратуры. Обнаружение отказа должно происходить в течение заданного интервала времени. Эту задачу решают внутрипроцессорный и межпроцессорный контроль.

Наиболее эффективно внутрипроцессорный контроль осуществляется путем тестирования в отведенные для этого промежутки времени или путем применения принципов самоконтроля (самопроверяемости) и сигнатурного анализа. Межпроцессорный контроль состоит во взаимной проверке работы процессоров на уровне системных шин, памяти и выходов (контроль с сильными связями). При контроле с умеренными

связями производится проверка выходов. Применяется также вариант, когда один процессор реализует вычисления, а другой их проверяет (контроль со слабыми связями).

Далее рассматриваются реально используемые на практике восемь основных типов безопасных структур.

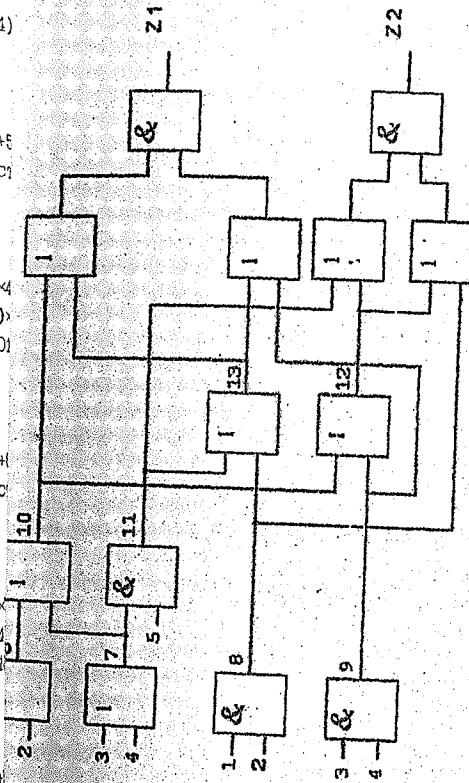

### 3.1 Структуры безопасных микропроцессорных модулей

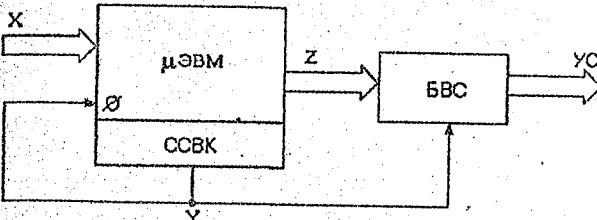

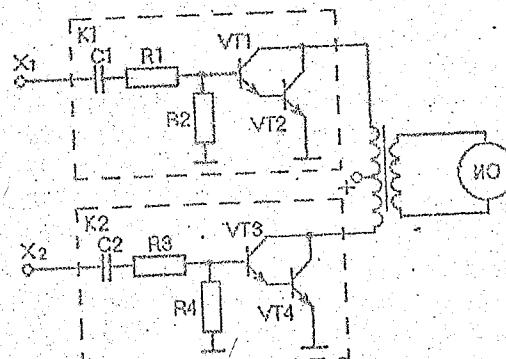

Одноканальная система с одной программой (тип 1) может быть применена при организации достаточно полной проверки микроЭВМ с помощью самопроверяемых средств внутреннего контроля (ССВК) и наличия (см. рисунок 3.1) безопасных выходных схем (БВС) для включения управляемых объектов [3.2], [3.3]. При возникновении отказа ССВК формирует сигнал  $Y$ , с помощью которого система может быть переведена в защитное состояние по выходу (например отключено питание) и (или) выходы микроЭВМ  $Z$  отключаются от управляемых объектов  $YO$  (с помощью БВС). Безопасность данной структуры зависит от эффективности способа самопроверки. Тестовые программы должны выполняться достаточно часто. Прикладные программы должны быть свободны от ошибок при загрузке. Целесообразно применение самопроверяемого программного обеспечения [3.3].

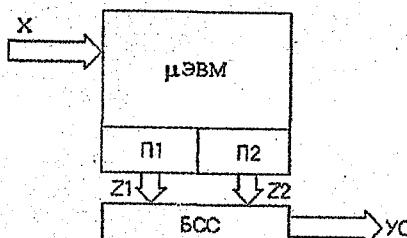

Одноканальная система с дублированной программой (тип 2) использует две различные и независимые программы (рисунок 3.2) для реализации одних и тех же функций [3.4], [3.5]. Результаты выполнения программ  $Z1$  и  $Z2$  сравниваются внешней безопасной схемой сравнения (БСС). Уровень безопасности зависит от степени различия двух программ и от интервала времени обращения к данным. Целесообразно, чтобы программы были написаны разными бригадами программистов и по разным алгоритмам.

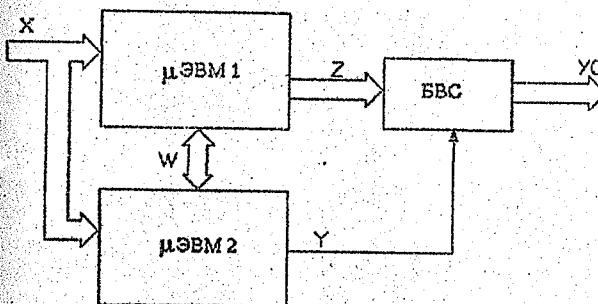

Дублированная система со слабыми связями (тип 3) состоит из двух микроЭВМ (рисунок 3.3), в которых процессоры и программы могут быть неодинаковыми [3.6], [3.7]. Процессор микроЭВМ 1 реализует основные вычисления, микроЭВМ 2 их проверяет. Для этого осуществляется обмен информацией по шине  $W$ . Синхронизация каналов необязательна. Контроль работы микроЭВМ осуществляется либо за счет тестовых программ, либо за счет параллельных вычислений и

Рисунок 3.1

Рисунок 3.2

Рисунок 3.3

РТМ 32 ЦШ 1115842.01-94

сравнения результатов. При обнаружении ошибки микроЭВМ 2 формирует сигнал  $Y$  и выходы микроЭВМ 1 отключаются от УО. В таких структурах возникают проблемы с обеспечением необходимой достоверности контроля.

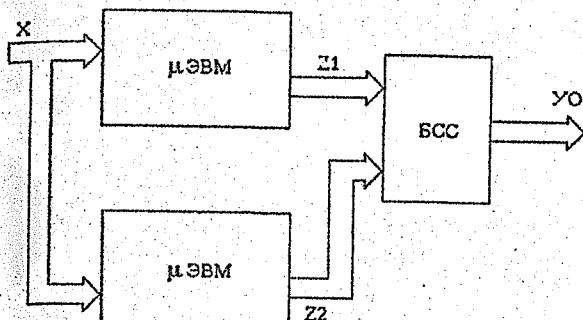

Дублированная система с умеренными связями (тип 4) включает в себя две одинаковые микроЭВМ (рисунок 3.4) с одинаковыми программами [3.8], [3.9]. Работа обоих каналов синхронизирована. Сравнение результатов обработки информации осуществляется на уровне выходов  $Z_1$  и  $Z_2$  с помощью БСС. Это одна из наиболее распространенных на практике безопасных структур. Минимальная кратность обнаруживаемых отказов в ней равна 2 - по одному отказу в каждой микроЭВМ, которые одинаковым образом искажают выходные сигналы  $Z_1$  и  $Z_2$ . Прикладные программы должны быть свободны от ошибок при загрузке. Одиночные отказы не опасны. Кратные независимые отказы могут не учитываться, если время обнаружения отказа достаточно мало.

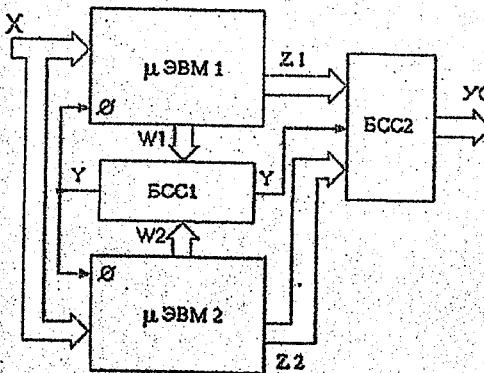

Дублированная система с сильными связями (тип 5) использует одинаковые программы в двух одинаковых микроЭВМ (рисунок 3.5), но в отличие от структуры типа 4 контроль работы двух каналов осуществляется здесь не только на уровне выходов, но и на уровне шин и памяти [3.7], [3.10]-[3.12]. Работа каналов синхронизирована. В наиболее сильном случае производится потактовая проверка совпадения сигналов  $W_1$  и  $W_2$  на внутренних контрольных точках (шинах) с помощью БСС 1. При возникновении ошибки сигнал  $Y$  воздействует на БСС 2 и отключает УО, т.е. переводит оба канала в защитное состояние. Структура обладает высоким уровнем безопасности. Проблему могут составить одинаковые программные ошибки в каналах.

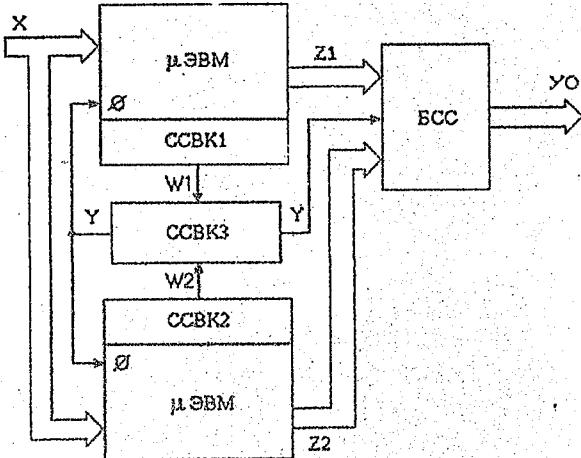

Самопроверяемая дублированная система (тип 6) состоит из двух каналов (рисунок 3.6), построенных в виде самопроверяемых устройств [3.3], [3.13], [3.14]. Сигналы контроля  $W_1$  и  $W_2$ , формируемые с помощью ССВК 1 и ССВК 2, сравниваются с ССВК 3. Последняя вырабатывает сигнал ошибки  $Y$ . Минимальная кратность обнаруживаемых отказов равна 4 - по два отказа в каждом канале, которые не обнаруживаются ССВК и одинаковым образом искажают выходные сигналы  $Z_1$  и  $Z_2$ . Самоконтроль каналов может быть аппаратный и

РТМ 32 ЦШ 1115842.01-94

Рисунок 3.4

Рисунок 3.5

Рисунок 3.6

Рисунок 3.7

РТМ 32 ЦШ 1115842.01-94

программный. Возможно использование независимых программ в каждом процессоре.

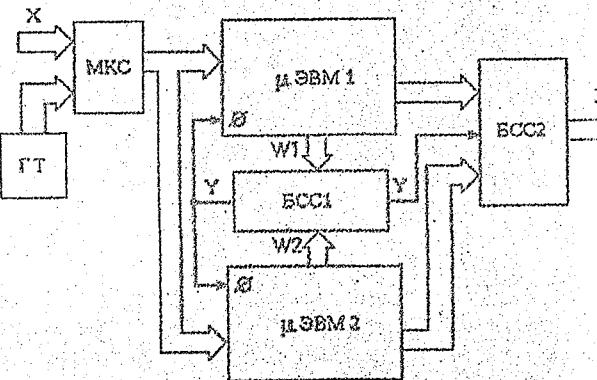

Дублированная система с тестированием и сильными связями (рисунок 3.7) содержит в дополнение к структуре типа 5 генератор тестов (ГТ) и мультиплексор (МКС) и применяется, если множество входных воздействий  $X$  не обеспечивает необходимой глубины проверки каналов обработки информации [3.15]. В этом случае в процессе рабочего функционирования периодически выделяются отрезки времени, в течение которых с помощью мультиплексора сигналы  $X$  отключаются от входов системы и к последним подключается генератор тестов. Результаты тестирования обоих каналов сравниваются БСС 1. При обнаружении ошибки система переводится в заливное состояние. Данный принцип используется также тогда, когда система большую часть рабочего функционирования находится в ходуемом режиме (при этом сигналы  $X$  длительное время не изменяются).

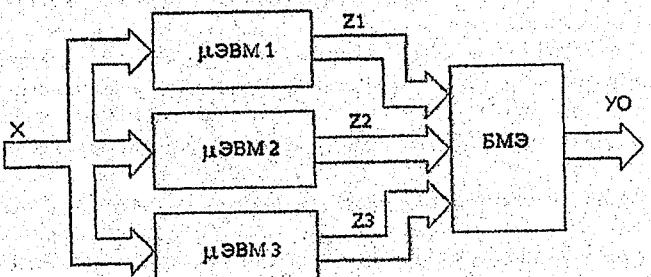

Троированная мажоритарная система (тип 8, рисунок 3.8) имеет три независимых канала обработки информации [3.2]-[3.7], [3.16], [3.17]. Работа каналов синхронизирована и сравнивается с помощью безопасного мажоритарного элемента (БМЭ). Безопасность сравнима с безопасностью дублированной структуры (рисунок 3.4), но отказоустойчивость увеличивается.

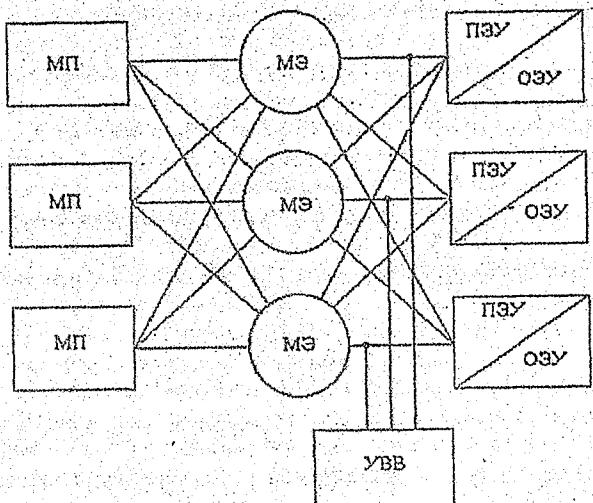

С применением в СЖАТ средств вычислительной техники появились специфичные структуры мажоритарно-резервированных МП на уровне двунаправленных шин (рисунок 3.9) [3.18]. Такой подход в построении МП СЖАТ требует разработки сложного специализированного модуля.

Рассмотренные структуры и принципы построения безопасных систем могут использоваться в сочетании, дополняя друг друга. При этом базовыми обычно являются дублированная (тип 4) и троированная (тип 8) структуры. Перспективным, на наш взгляд, является принцип построения самопроверяемых систем (тип 6).

### 3.2 Аппаратный контроль и способы локализации отказов микропроцессорных систем автоматики

Как уже отмечалось, в СЖАТ, выполненных на основе МП и мик-

РТМ 32 ЦШ 1115842.01-94

Рисунок 3.8

Рисунок 3.9

РТМ 32 ЦШ 1115842.01-94

роЭВМ, необходимо использовать структурное резервирование и аппаратный контроль [3.19].

Обмен информацией между отдельными узлами микроЭВМ, входящих в состав микрэлектронных систем (МЭС), осуществляется через шины внутреннего интерфейса, поэтому при контроле совпадения сигналов на этих шинах можно утверждать, что они в процессе выполнения рабочих и тестовых алгоритмов функционируют без отказов, т.е. таким образом можно контролировать исправность внутренних функциональных узлов микроЭВМ [3.20]. Для сравнения результатов обработки информации используют компараторы с несимметричной характеристикой отказов.

Устройство сравнения и п-резервированные каналы обработки информации выполняются в виде конструктивно законченного безопасного модуля.

В большинстве случаев устройство контроля шин внутреннего интерфейса МП не определяет, какой узел отказал, а просто фиксирует расхождение в работе каналов обработки информации и первоначально, для того чтобы отличить сбой от отказа, осуществляет перезапуск искаженного участка программы во всех п-микроЭВМ. При повторном обнаружении неравнозначности кодовых векторов на шинах микроЭВМ осуществляется реконфигурация безопасного МП-модуля или устройство контроля обеспечивает безопасное (выключенное) состояние модуля. Причем отключение должно осуществляться необратимо даже в случае нового отказа в системе.

При выполнении рабочих алгоритмов МП СЖАТ некоторые элементы микроЭВМ могут использоваться с малой интенсивностью (например области ОЗУ и ПЭУ), поэтому для обеспечения большей глубины контроля и исключения возможности накопления отказов необходимо предусмотреть их циклическую тестовую проверку. Одним из видов такой проверки в паузах между эксплуатационными событиями является использование имитационных программ для тестового моделирования поездной обстановки на станции или перегоне. Таким образом, длительность периода контроля элементов МП-модуля определяется рабочими и тестовыми алгоритмами системы.

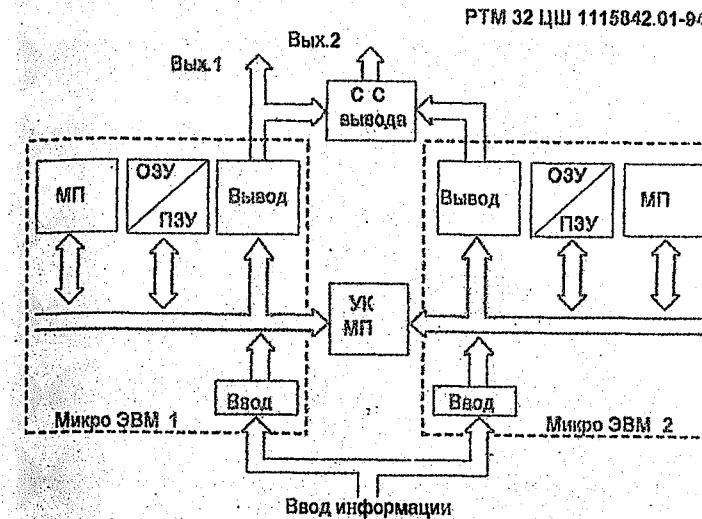

Как было показано в п. 3.1, для обеспечения безопасности МЭС достаточно дублирование структуры устройства. На рисунке 3.10

РТМ 32 ЦШ 1115842.01-94

приведена обобщенная структура дублированного МП-модуля. Шины внутреннего интерфейса контролируются компаратором с несимметричной характеристикой отказов (УК МП) [3.20].

Выходная информация на внешнем интерфейсе может формироваться схемами сравнения (вых.1) или с выхода одной из микроЭВМ (вых.2). Во втором случае необходимо дополнительное устройство, контролирующее идентичность состояния выходов обоих микроЭВМ.

УК выходов МП-модуля может быть также общим, но при этом отказ любого выходного элемента приводит к отказу всего модуля. Поэтому в ряде случаев целесообразно выходы внешнего интерфейса разделять на группы, имеющие свое устройство контроля, или внешний интерфейс организовывать на элементах И, ИЛИ с несимметричной характеристикой отказов. В этих случаях МЭС, выполненная на основе дублированной микроЭВМ, обладает функциональной отказоустойчивостью, т.к. при отказе некоторых выходов она частично сохраняет свою работоспособность.

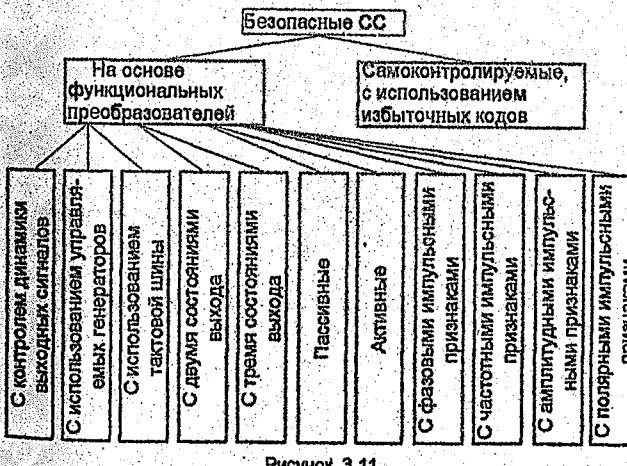

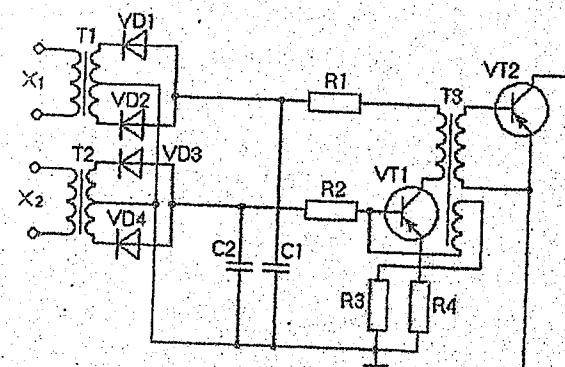

В настоящее время известно довольно много безопасных схем сравнения с несимметричной характеристикой отказа, исключающих ложный логический сигнал 1 на выходе [3.10], [3.20]. Классификация безопасных компараторов приведена на рисунке 3.11.

В компараторах на основе функциональных преобразователей, получивших наибольшее распространение, несимметричность отказов достигается за счет того, что при отказе их элементов нарушается закон преобразования сигналов из одного вида в другой. В этом случае на их выходе сигнал отсутствует или появляется в виде, не воспринимаемом последующим элементом.

На основе анализа показателей надежности известных компараторов [3.20], применяемых для оправления кодовых векторов на шинах интерфейса в параллельном виде, можно сделать вывод, что одними из лучших являются самопроверяемые тестеры 2/4 [3.31].

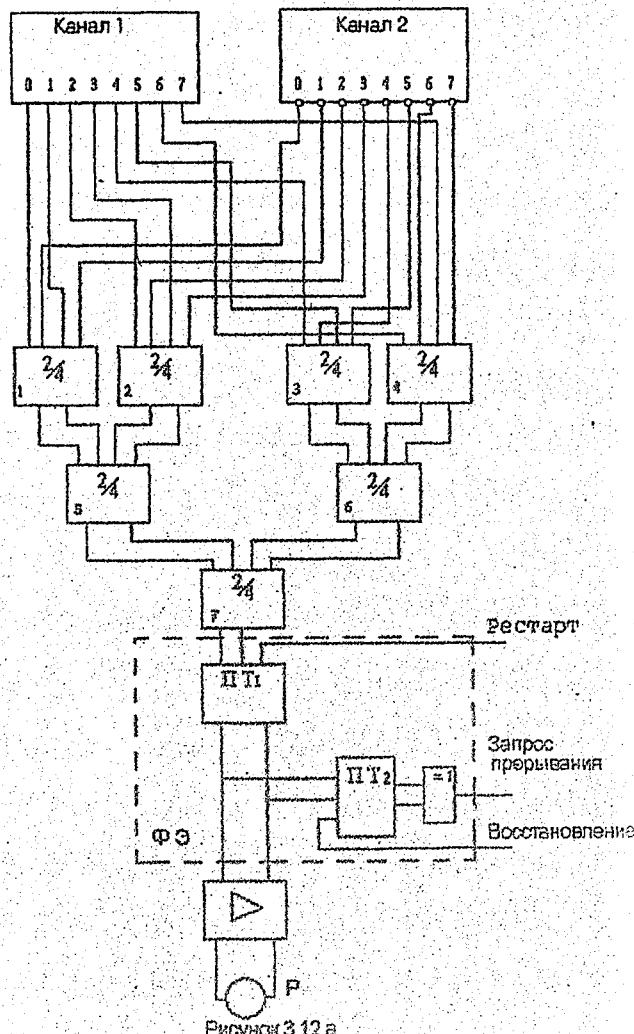

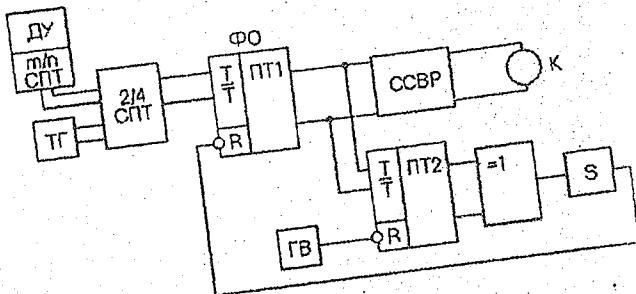

На рисунке 3.12а приведена функциональная схема устройства контроля шин дублированного МП-модуля. Сигналы от второго МП поступают в инверсном виде. При нарушении согласованной работы МП на выходах контрольных схем 2/4 (рисунок 3.12б) появляется непараллельный сигнал, что регистрируется фиксирующим элементом (ФЭ).

Для того чтобы отличать сбои и отказы аппаратуры, ФЭ состоит

Рисунок 3.10

Рисунок 3.11

28

из двух последовательно соединенных парафазных триггеров ПТ<sub>1</sub> и ПТ<sub>2</sub> [3.21]. При первоначальном нарушении парафаиности на выходах контрольных схем оба ПТ блокируются и в МП поступает запрос прерывания. По этому сигналу в МП осуществляется возврат в программе на несколько шагов назад (рестарт), формируется сигнал восстановления ПТ<sub>1</sub> и искаженный участок программы повторяется вновь. Если снова фиксируется нарушение идентичности выполнения программы, то ПТ<sub>1</sub> окончательно блокируется и контактами реле Р выключается питание МП-модуля, т.е. обеспечивается защитное состояние МЭС. При отсутствии повторного сбоя, т.е. при полном прохождении первоначально искаженного программного блока, МП формируют сигнал восстановления ПТ<sub>2</sub>.

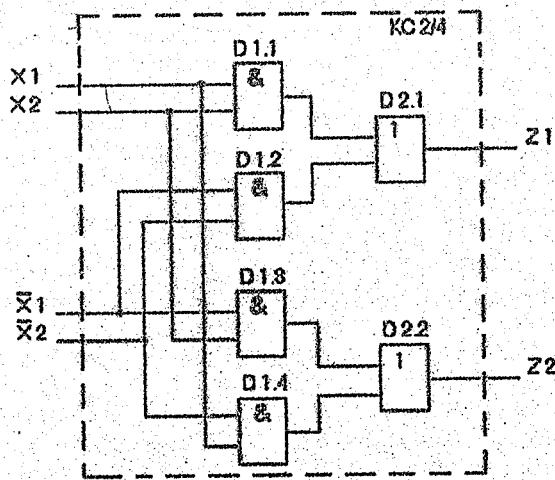

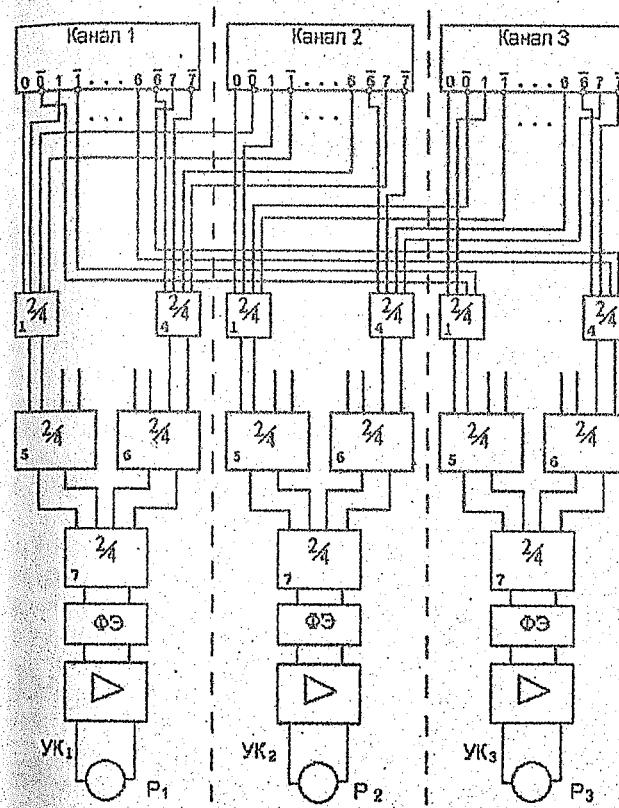

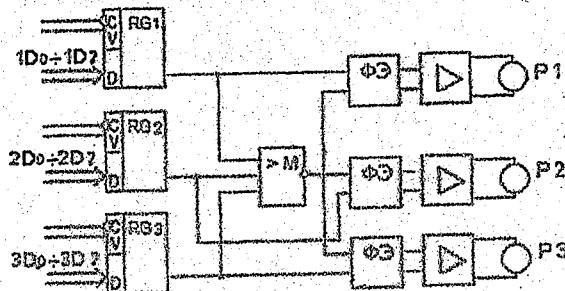

На основе самопроверяемых тестеров выполнено устройство контроля шин трехканального микропроцессорного модуля (рисунок 3.13). Сигналы на шинах МП попарно сравниваются, так же как и в дублированной структуре, с помощью тестеров 2/4. При отказе одного из МП выключаются два контрольных реле и с помощью их контактов осуществляется дешифрация номера неисправного канала и его отключения.

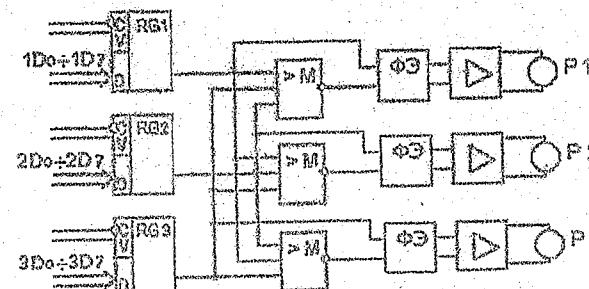

Сократить число элементов и значительно повысить надежность устройства контроля МП-модулей можно за счет сравнения кодовых векторов ячеек шин не в параллельном виде, а в последовательном. С этой целью для мультиплексирования сигналов на шинах МП используются универсальные сдвиговые регистры. На рисунках 3.14-3.16 предлагаются структурные схемы устройств контроля шин дублированных и мажоритарно-резервированных МП-модулей.

В УК, приведенных на рисунках 3.15, 3.16, не требуется дешифратор неисправного канала, т.к. контрольное реле подключено к соответствующему каналу обработки информации.

С целью повышения отказоустойчивости МЭС в УК, предлагаемом на рисунке 3.16, мажоритарный элемент контроля выполнен резервированным.

Таким образом, можно сделать вывод, что УК шин внутреннего интерфейса обеспечивает большую глубину диагностирования по сравнению с контролем внешнего интерфейса микроЭВМ, т.е. дает возмож-

РТМ 32 ЦШ 1116842.01-94

Рисунок 9.12 б

PTM 32 ЦШ 1115842.01-94

Рисунок 3.13

ность последовательно во времени сравнивать сигналы всех узлов вычислительных каналов.

#### 4 ПРИНЦИПЫ ПОСТРОЕНИЯ БЕЗОПАСНЫХ СХЕМ НА ЭЛЕМЕНТАХ С НЕСИММЕТРИЧНЫМИ ОТКАЗАМИ

##### 4.1 Элементы о несимметричными отказами

С точки зрения безопасности элементы, на которых осуществляется построение безопасных систем, делятся на элементы с симметричными отказами и элементы о несимметричными отказами. У элементов о симметричными отказами вероятности возникновения отказов видов  $0 \rightarrow 1$  и  $1 \rightarrow 0$  примерно равны (имеют один порядок). К ним относятся большинство элементов, используемых в микрэлектронной и микропроцессорной технике. У элементов с несимметричными отказами интенсивности отказов разного вида различаются на порядок и более. Если при этом интенсивность отказов не более некоторого критического значения при заданном уровне безопасности ( $\lambda_{кр} \sim 10^{-8} \div 10^{-14} 1/ч$ ), то элемент называют безопасным.

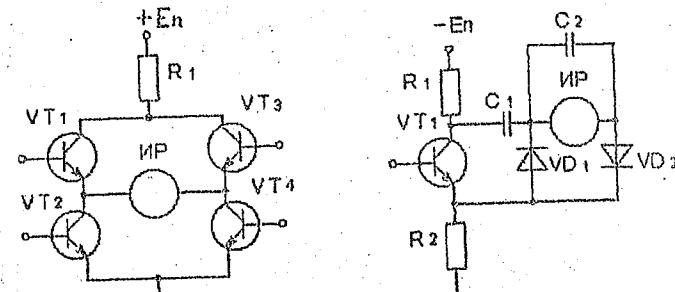

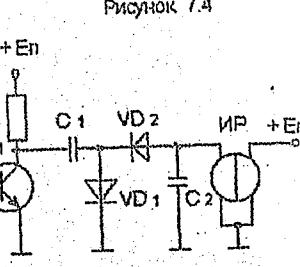

Безопасные элементы разрабатываются специально для построения безопасных систем. Несимметричность отказов достигается сочетанием следующих основных методов: соответствующим физическим представлением логических сигналов; реаэрвированием деталей и узлов; специальными конструктивными мерами; импульсным кодированием логических сигналов; использованием генераторных и резонансных режимов работы; гальванической развязкой входных и выходных цепей.

Безопасные элементы бывают двух типов: элементы, надежные относительно отказов вида  $0 \rightarrow 1$  ( $h_1$ -надежные), и элементы, надежные относительно отказов вида  $1 \rightarrow 0$  ( $h_0$ -надежные). На практике обычно используются  $h_1$ -надежные элементы. Методы построения безопасных схем на  $h_1$ -надежных и  $h_0$ -надежных элементах один и те же.

##### 4.2 Принципы построения безопасных комбинационных схем

Безопасная комбинационная схема задается с помощью двух

Рисунок 3.14

Рисунок 3.15

Рисунок 3.16

функций алгебры логики (ФАЛ): функции  $f$ , которую схема должна реализовать, и функции опасного отказа  $f_{\text{оп}}$ , равной единице на опасных входных наборах. Опасным входным набором называется множество значений входных переменных, при наличии которых отказ вида  $0 \rightarrow 1$  на выходе схемы приводит к опасному искаложению алгоритма функционирования. Отказ, при котором функция  $f'$ , реализуемая неисправной комбинационной схемой, и  $f_{\text{оп}}$  равны 1 хотя бы на одном общем входном наборе, называется опасным отказом.

Таким образом, для опасного отказа выполняется условие:

$$f' \cdot f_{\text{оп}} \neq 0. \quad (4.1)$$

В большинстве практических случаев считается, что  $f_{\text{оп}} = f$ . Тогда безопасной называется комбинационная схема, которая вполне надежна относительно отказов вида  $0 \rightarrow 1$  ( $h_1$ -надежная схема). В дальнейшем рассматриваются именно такие схемы.

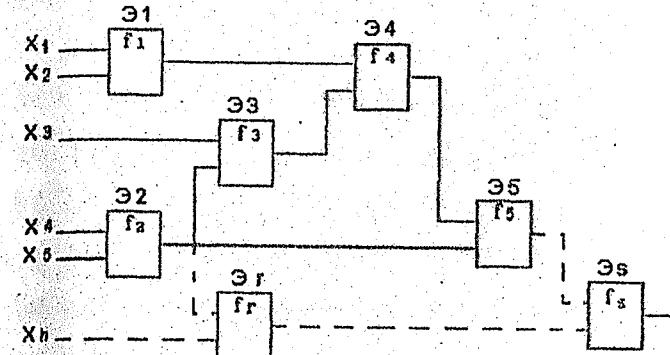

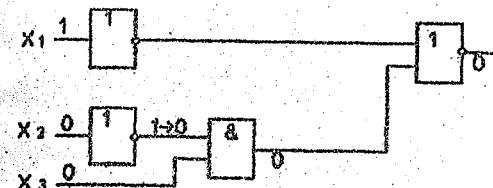

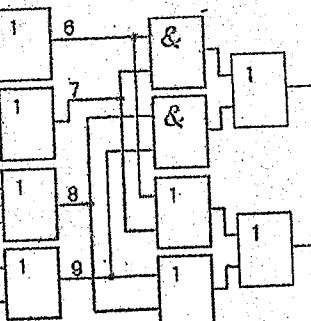

Сформулируем требования к безопасным комбинационным схемам. Пусть имеется произвольная схема, содержащая безопасные логические элементы  $\mathcal{E}_1, \mathcal{E}_2, \dots, \mathcal{E}_5$  (рисунок 4.1), каждый из которых реализует некоторую функцию  $f_1, f_2, \dots, f_5$ . Присвоим каждому элементу свой ранг. Первый ранг имеют элементы, соединенные только со входами схемы. Ранг  $g$  имеют элементы, входы которых соединены с выходами элементов с рангом не выше  $g-1$ . В схеме (рисунок 4.1) первый ранг имеют элементы  $\mathcal{E}_1$  и  $\mathcal{E}_2$ , второй ранг -  $\mathcal{E}_3$ , третий -  $\mathcal{E}_4$ , четвертый -  $\mathcal{E}_5$  и т.д.

Следующая теорема определяет способ построения безопасных схем.

**ТЕОРЕМА 4.2.1.** Неизбыточная комбинационная схема, построенная на безопасных элементах, является безопасной тогда и только тогда, когда все ее элементы ранга  $K \geq 2$  реализуют монотонные функции алгебры логики.

Функция называется монотонной, если для двух любых двоичных наборов  $a = (a_1, a_2, \dots, a_n)$  и  $b = (b_1, b_2, \dots, b_n)$  из условия  $a < b$  следует, что  $f(a) \leq f(b)$ . Особенностью монотонной функции является то, что ее минимальная дизъюнктивная форма (МДНФ) не содержит переменных с отрицанием. Это в свою очередь определяет следующее свойство схемы, реализующей монотонную функцию (рисунок 4.2): если на входе схемы произошла смена сигнала  $1 \rightarrow 0$ , то на выходе

Рисунок 4.1

Рисунок 4.2

Рисунок 4.3

схемы может произойти смена сигналов  $1 \rightarrow 0$ , но не может произойти смена сигналов  $0 \rightarrow 1$ .

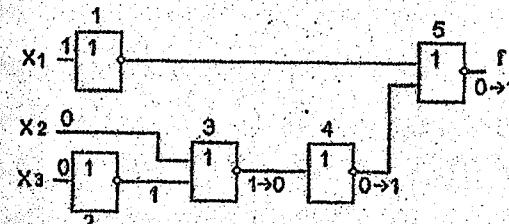

Рассмотрим схему (рисунок 4.3) на безопасных элементах И, ИЛИ, НЕ, для которой не выполняется требование теоремы 4.2.1. В ней элемент 4 третьего ранга реализует немонотонную ФАЛ (инверсию). Схема вычисляет функцию

$$f = x_1 \vee x_2 \vee x_3. \quad (4.2)$$

Рассмотрим работу схемы на двоичном наборе 100,  $f(100)=0$ . Пусть произойдет отказ элемента 3 вида  $1 \rightarrow 0$ . Элемент 4 инвертирует вид отказа, т. е. на его выходе будет происходить изменение сигнала  $0 \rightarrow 1$ . Это же изменение сигнала будет и на выходе схемы. Следовательно, схема не является безопасной ( $h_1$ -надежной).

Для выполнения требования теоремы 4.2.1 надо преобразовать формулу (4.2), применив правило де Моргана:

$$f = x_1 \vee x_2 \vee x_3. \quad (4.3)$$

Формула (4.3) имеет знаки отрицания только над переменными. Это означает, что в соответствующей ей схеме элементы НЕ являются только элементами первого ранга (см. рисунок 4.4). Поэтому изменение сигнала вида  $1 \rightarrow 0$  на какой-либо внутренней линии схемы не может перейти в изменение вида  $0 \rightarrow 1$  на выходе, и схема является  $h_1$ -надежной. При этом сами входные датчики, формирующие сигналы  $x$ , должны быть  $h_1$ -надежными и не давать ложной информации вида  $0 \rightarrow 1$ .

Теорема 4.2.1 накладывает весьма жесткие ограничения на способы построения безопасных комбинаторных схем. Это следует из того, что единственными формами представления функций алгебры логики, у которых немонотонная операция применяется только к переменным функции, являются дизъюнктивная нормальная форма (ДНФ), конъюнктивная нормальная форма (КНФ) и их скобочные формы СДНФ, СКНФ. Поэтому имеет место:

**Теорема 4.2.2.** Схемная реализация функции алгебры логики является безопасной тогда и только тогда, когда она осуществлена по одной из четырех форм представления функции: ДКФ, КНФ, СДНФ и СКНФ.

РУССКАЯ

Psychology

Рынок

Рисунок 4.7

### 4.3 Функциональная полнота безопасных элементов

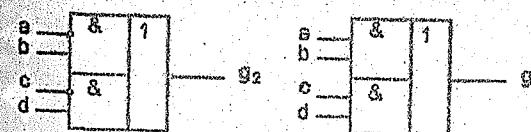

Рассмотрим вопрос о функциональной полноте безопасных элементов. Пусть имеется система функций  $A = \{g_1, g_2, \dots, g_k\}$ .

**Определение 4.3.1.** Система функций  $A$  называется безопасно полной (безопасным базисом), если с помощью логических элементов, реализующих безопасно функции этой системы, можно реализовать безопасно любую функцию алгебры логики.

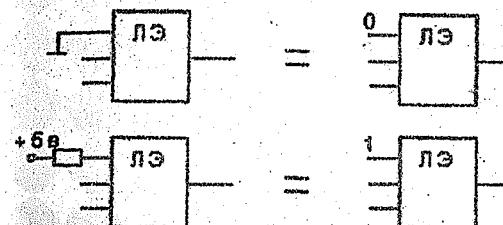

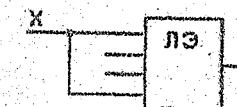

Система  $A$  может содержать и константы 0 и 1. Они реализуются соединением входов элементов с полюсами источников питания (рисунок 4.5). Надежность реализации констант определяется надежностью монтажных соединений. Это же относится к надежности реализации функции X (повторения), которая осуществляется за счет отождествления входов элементов монтажным соединением их между собой (рисунок 4.6).

Условия функциональной полноты безопасных элементов определяет следующая теорема.

**ТЕОРЕМА 4.3.1.** При наличии вполне надежных констант и надежного отождествления входов система  $A$  является безопасно полной тогда и только тогда, когда выполняются следующие условия:

- 1) система  $A$  содержит хотя бы одну немонотонную функцию;

- 2) система  $A$  содержит: а) монотонную функцию, которая не является дизъюнкцией или конъюнкцией, или б) конъюнкцию и дизъюнкцию.

Пусть задана система, которая удовлетворяет условиям теоремы:

$A = \{0, 1, g_1, g_2, g_3\}$ , где  $g_1 = a$ ,  $g_2 = ab \vee cd$ ,  $g_3 = ab \vee cd$ . Функция  $g_2$  является немонотонной, а функция  $g_3$  - монотонной и отличной от дизъюнкции и конъюнкции.

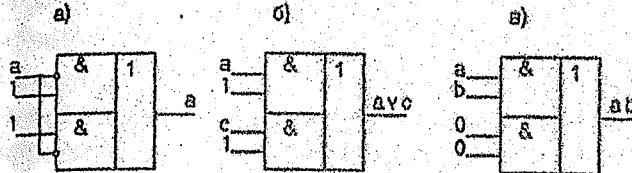

Функции  $g_2$  и  $g_3$  реализуются безопасными элементами (рисунок 4.7). Построим на этих элементах безопасную схему, вычисляющую функцию  $f = (a \vee b)c \vee abd$ . На рисунке 4.8, а, б, в показана реализация соответственно функций НЕ, ИЛИ, И. Они образуют безопасно полный набор элементов. Искомая реализация функции приведена на рисунке 4.9.

Если монтажные соединения не являются вполне надежными, то справедлива следующая теорема.

**ТЕОРЕМА 4.3.2.** При отсутствии вполне надежных констант и на-

Рисунок 4.8

Рисунок 4.9

даждного отождествления входов система А является безопасно полной тогда и только тогда, когда она содержит функции И, ИЛИ, НЕ.

#### 4.4 Принципы построения безопасных схем с памятью на безопасных элементах

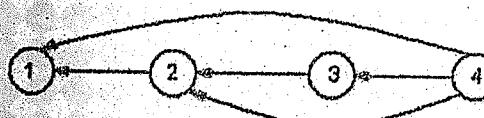

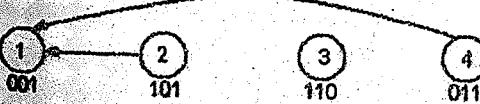

Исходными данными для синтеза безопасного автомата (схемы с памятью) являются таблица переходов и граф безопасных ложных переходов.

Принципы построения рассмотрим на примере синтеза синхронного автомата, заданного таблицей 4.4.1 и рисунком 4.10. В таблице 4.4.2 приведена кодированная таблица переходов, использующая один из вариантов безопасного кодирования состояний.

Таблица 4.4.1

| S | a   |     | Z |

|---|-----|-----|---|

|   | 0   | 1   |   |

| 1 | (1) | 2   | 0 |

| 2 | 3   | (2) | 0 |

| 3 | (3) | 4   | 0 |

| 4 | (4) | (4) | 1 |

Таблица 4.4.2

| S | y  | y    | x    |   | Z |

|---|----|------|------|---|---|

|   |    |      | 0    | 1 |   |

| 1 | 00 | (00) | 01   | 0 |   |

| 2 | 01 | 10   | (01) | 0 |   |

| 3 | 10 | (10) | 11   | 0 |   |

| 4 | 11 | (11) | (11) | 1 |   |

Граф возможных ложных переходов для этого варианта (рисунок 4.11) является субграфом графа безопасных ложных переходов (рисунок 4.10).

Построим безопасный автомат, используя безопасные элементы И, ИЛИ, НЕ и безопасный D-триггер (в качестве элемента памяти). По таблице 4.4.2 находим логические функции, описывающие схему автомата:

Рисунок 4.10

Рисунок 4.11

Рисунок 4.12

РТМ 32 ЦШ 1115842.01-94

$$y_1 = x_{u_1} \vee x_{u_2} \vee x_{u_1 u_2} \vee y_{1u_2};$$

$$y_2 = x \vee y_{1u_2};$$

$$z = y_1 y_2.$$

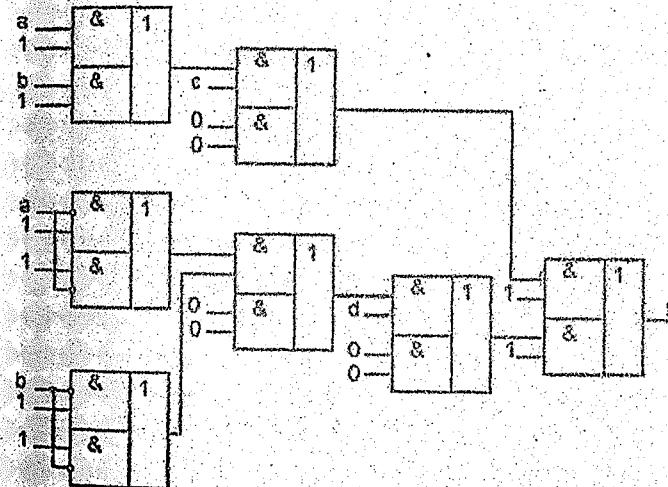

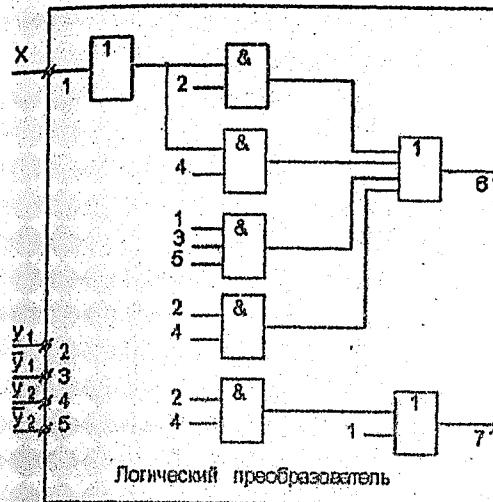

На рисунках 4.12 и 4.13 показана реализация данной системы функций. При этом логический и выходной преобразователи построены как  $h_1$ -надежные схемы. Покажем, что в схеме автомата отсутствуют опасные отказы. Необходимо рассмотреть три типа отказов:

1) отказы D-триггеров вида  $1 \rightarrow 0$  не опасны, т. к. применено безопасное кодирование;

2) отказы элементов логического преобразователя вида  $1 \rightarrow 0$  приводят к изменению сигналов на выходах логического преобразователя в такте вида  $1 \rightarrow 0$ , что вызывает ложное переключение D-триггеров вида  $1 \rightarrow 0$ ; это не опасно по п.1;

3) отказы элементов выходного преобразователя вида  $1 \rightarrow 0$  не опасны, поскольку последний построен как  $h_1$ -надежная схема.

Часто для получения безопасного кодирования необходимо вводить избыточность по числу элементов памяти. Например, если из графа безопасных ложных переходов (рисунок 4.10) исключить ложный переход  $3 \rightarrow 1$  (рисунок 4.14), то в этом случае нельзя найти безопасное кодирование с использованием элементов памяти.

Введем третий дополнительный элемент памяти и применим вариант безопасного кодирования, показанный в таблице 4.4.3. Граф возможных искажений показан на рисунке 4.15. При этом возникает проблема доопределения неосновных состояний таким образом, чтобы исключить опасные отказы.

В таблице 4.4.3 приведен наиболее простой из возможных способов доопределения: во всех клетках неосновных состояний проставляется код  $000\dots 00$  и значение выхода  $Z=0$ . При таком кодировании любой отказ вида  $1 \rightarrow 0'$ , который переводит схему из основного состояния в неосновное, в конце концов переводит схему в защитное необратимое состояние  $000\dots 00$ . На рисунке 4.16 показан процесс перехода схемы в необратимое состояние, если она находилась в устойчивом состоянии  $(0,110)$  и произошел отказ элемента памяти вида  $1 \rightarrow 0$ .

РТМ 32 ЦШ 1115842.01-94

Рисунок 4.13

Рисунок 4.14

Рисунок 4.15

Таблица 4.4.3

|                      | S | у у у | x     |       | Z |

|----------------------|---|-------|-------|-------|---|

|                      |   |       | 0     | 1     |   |

| Основные состояния   | 1 | 0 0 1 | (001) | 101   | 0 |

|                      | 2 | 1 0 1 | 110   | (101) | 0 |

|                      | 3 | 1 1 0 | (110) | 011   | 0 |

|                      | 4 | 0 1 1 | (011) | (011) | 1 |

| Неосновные состояния | 5 | 0 0 0 | (000) | (000) | 0 |

|                      | 6 | 0 1 0 | 000   | 000   | 0 |

|                      | 7 | 1 0 0 | 000   | 000   | 0 |

|                      | 8 | 1 1 1 | 000   | 000   | 0 |

Любой ложный переход в защитное необратимое состояние опасен, т. к. в этом состоянии отключаются все выходы. Выход схемы из него в основное начальное состояние производится искусственно путем по цепям установки. Защитное необратимое состояние может находиться и среди основных состояний схемы. Примером такого состояния является окончательное замыкание стрелок и сигналы в схемах электрической централизации. Выход из него осуществляется с помощью искусственной разделки марпрутов.

В итоге можно сформулировать следующие основные принципы построения безопасных автоматов на безопасных элементах: 1) для кодирования состояний автомата выбирается один из вариантов безопасного кодирования; 2) для всех неосновных состояний автомата определяется переход в защитное необратимое состояние; 3) все

неосновным состояниям приписываются значения выходов Z=0; 4) логический и выходной преобразователи строятся как безопасные схемы в соответствии с условиями теоремы 4.2.1.

## 5 ИСПОЛЬЗОВАНИЕ САМОПРОВЕРЯЕМЫХ СХЕМ ПРИ ПОСТРОЕНИИ БЕЗОПАСНЫХ СИСТЕМ

### 5.1 Структура самопроверяемого дискретного устройства

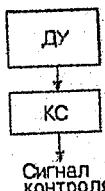

Самопроверяемые дискретные устройства (ДУ) относятся к классу систем с контролем в процессе функционирования.

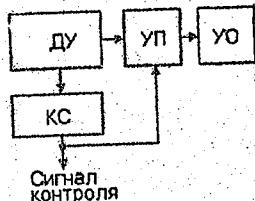

Самопроверяемые ДУ содержат два блока (рисунок 5.1). Первый блок (существенно ДУ) реализует функции переходов и выходов. Второй блок (КС) представляет собой контрольную схему, назначение которой состоит в выработке сигнала контроля при возникновении неисправностей во внутренней структуре ДУ.

Контрольная схема рассматривается как элемент собственно структуры ДУ, выход контрольной схемы - как контрольный выход ДУ.

### 5.2 Принципы использования самопроверяемых ДУ в безопасных системах

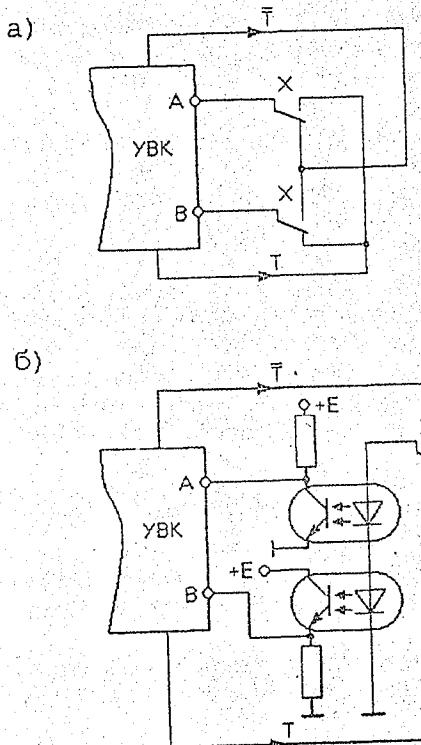

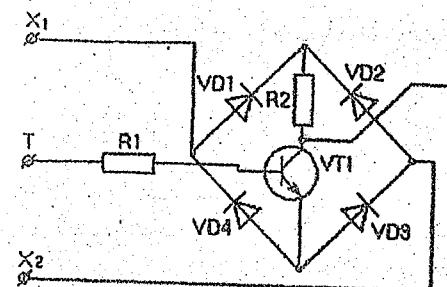

Сигнал контроля используется для отключения объектов управления (OU) с помощью специальных устройств переключения (УП), которые должны иметь несимметричные отказы (рисунок 5.2).

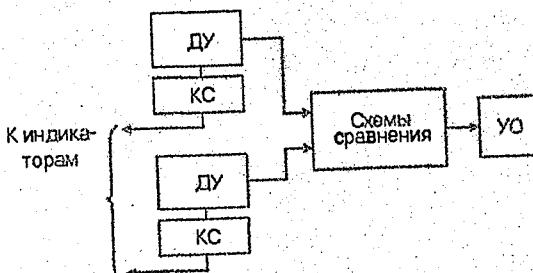

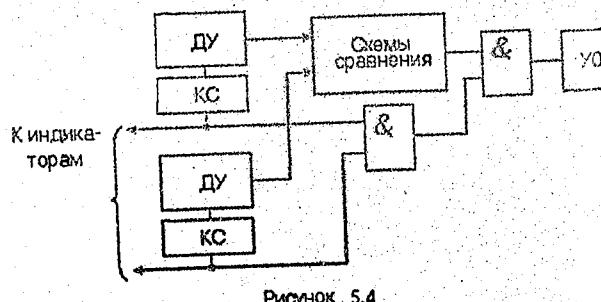

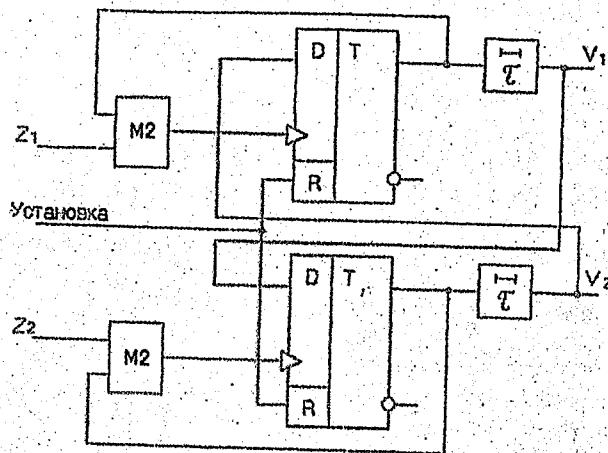

В резервированных системах (дублированных, троированных) сигнал контроля используется для определения отказавшего комплекта аппаратуры (рисунок 5.3) и/или для дополнительного отключения выходов (рисунок 5.4), что позволяет увеличить кратность обнаруживаемых неисправностей (в дублированных системах - до четырех).

### 5.3 Принципы контроля ДУ

Основной принцип состоит в кодировании состояний ДУ кодом с обнаружением ошибок. Свойства ДУ определяются свойствами кода, использованного для кодирования внутренних состояний.

Рисунок 5.1

Рисунок 5.2

Рисунок 5.3

Рисунок 5.4

Эффективным является использование для кодирования кода с постоянным весом  $m$  ( $nSm$ -кода,  $n$  - число разрядов кодовых слов). В этом случае обеспечивается обнаружение в схеме ДУ всех одиночных неисправностей; а также всех сочетаний односторонних одиночных неисправностей (т.е. неисправностей одного вида: либо  $1 \rightarrow 0$ , либо  $0 \rightarrow 1$ ).

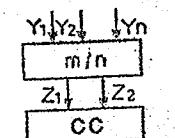

Контроль ДУ может осуществляться либо по внутреннему состоянию, либо по выходному состоянию. При использовании  $nSm$ -кода КС фиксирует все состояния и вырабатывает сигнал контроля при нарушении веса. В этом случае КС называют  $m/n$ -тестером.

#### 5.4 ДУ с контролем по внутреннему состоянию

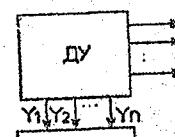

Структура ДУ представлена на рисунке 5.5. На входы  $m/n$ -тестера подаются внутренние переменные  $Y_1, Y_2, \dots, Y_n$  (выходы элементов памяти).

ДУ обладает следующим свойством. При нормальном функционировании ДУ и отсутствии в нём неисправностей на его основных выходах  $Y_1, Y_2, \dots, Y_r$  присутствует рабочее выходное состояние, а на контрольных выходах  $Y_1, Y_2, \dots, Y_n$  - вектор с весом  $m$ . При возникновении неисправности во внутренней структуре ДУ на основных выходах  $Y_1, Y_2, \dots, Y_r$  устанавливается некоторое (отличное от рабочего) защищённое состояние, а на контрольных выходах  $Y_1, Y_2, \dots, Y_n$  - вектор о весом, не равным  $m$ . При этом на выходе  $m/n$ -тестера формируется сигнал контроля.

#### 5.5 ДУ с контролем по выходному состоянию

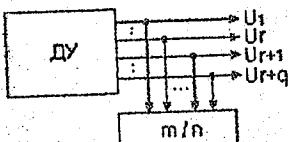

Структура ДУ представлена на рисунке 5.6. Выходные состояния кодируются кодом  $nSm$ . При необходимости вводятся дополнительные контрольные выходы  $V_{r+1}, \dots, V_{r+q}$ .

На входы  $m/n$ -тестера подаются выходные переменные ДУ. ДУ обладает следующим свойством. При нормальном функционировании ДУ и отсутствии в нем неисправностей на основных выходах  $V_1, V_2, \dots, V_r$  присутствует рабочее выходное состояние, на основных и контрольных выходах  $V_1, V_2, \dots, V_r, V_{r+1}, \dots, V_{r+q}$  - вектор с весом  $m$ . При

Рисунок 5.5

Рисунок 5.5

Рисунок 5.6

Рисунок 5.6

Рисунок 5.7

Рисунок 5.7

Рисунок 5.9

Рисунок 5.9

Рисунок 5.8

Рисунок 5.8

Рисунок 5.10

Рисунок 5.10

возникновении неисправности на основных выходах устанавливается защитное состояние, на основных и контрольных выходах - вектор с весом, не равным  $m$ . При этом на выходе  $m/n$ -тестера формируется сигнал контроля.

### 5.6 Самопроверяемое ДУ со свойством блокировки

Свойство блокировки связано с определением момента подавления и длительности присутствия сигнала контроля.

ДУ обладает свойством блокировки, если при возникновении в его структуре неисправности на основных и контрольных выходах устанавливается защитное состояние не позднее того такта, в котором неисправность в первый раз проявляется на выходе, после чего защитное состояние сохраняется до тех пор, пока в ДУ не возникает новая неисправность. Соответственно в указанные моменты времени на выходе контрольной схемы присутствует сигнал контроля.

Принцип построения ДУ с блокировкой состоит в следующем. Внутреннее состояние ДУ кодируется кодом  $pS_n$ . Это позволяет выделить на всем множестве внутренних состояний подмножество  $S$  основных состояний и подмножество  $R$  ошибочных (защитных) состояний. Логическая сеть ДУ строится таким образом, что любая одиночная неисправность или любая комбинация одиночных односторонних неисправностей переводит ДУ из множества  $S$  в множество  $R$ . После этого ДУ блокируется в множестве  $R$ , т.е. оно может выйти из множества  $R$  только искусственным путем (по цепям установки элементов памяти) или при возникновении новых отказов. Состояниям из множества  $R$  ставятся в соответствие защитные значения выходов. Переход автомата в множество  $R$  фиксируется контрольной схемой.

### 5.7 Определение самопроверяемого ДУ

Сформулируем указанные свойства самопроверяемых ДУ в терминах теории автоматов. Выделим на полном множестве выходных  $Z$  и внутренних  $S$  состояний ДУ множества основных (рабочих) состояний  $Z$  и  $S$  и некоторые множества защитных (ошибочных) состояний  $Z_r$  и  $S_r$  таких, что  $Z \cup Z_r \subseteq Z$ ,  $Z \cap Z_r = \emptyset$ ,  $S \cup S_r \subseteq S$ ,  $S \cap S_r = \emptyset$ .

РТМ 32 ЦШ 1115842.01-94

Определение 5.7.1. ДУ называется защищенным от неисправностей, если при возникновении любой неисправности из заданного класса на любой рабочей входной последовательности выходные состояния либо вычисляются правильно, либо принадлежат множеству защитных состояний  $Z_r$ .

Определение 5.7.2. ДУ называется самотестируемым, если для каждой неисправности из заданного класса существует хотя бы одна рабочая входная последовательность, на которой появляется хотя бы одно выходное состояние, принадлежащее множеству защитных состояний  $Z_r$ .

Определение 5.7.3. ДУ называется полностью самоуправляемым (ПСП), если оно защищено от неисправностей и является самотестируемым.

Защищенность от неисправностей исключает неправильные воздействия со стороны управляющего ДУ на объекты управления. Это есть основное требование к безопасным системам (fail safe system). Свойство самотестируемости исключает наличие в схеме ДУ необнаруживаемых неисправностей из заданного класса и устраниет возможность их накопления. При этом рабочие входные воздействия составляют одновременно и проверяющий тест. Таким образом, ДУ, удовлетворяющее определениям 5.7.1 - 5.7.3, в указанном смысле само себя контролирует.

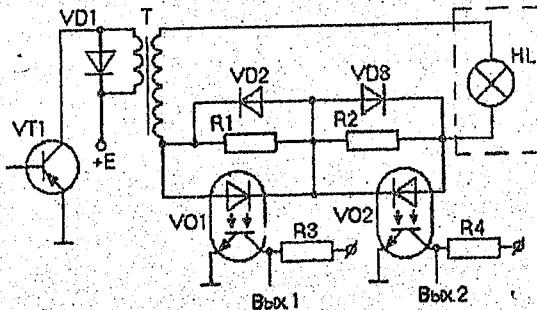

## 5.8 Самопроверяемые тестеры

Тестеры в самопроверяемых ДУ рассматриваются как элементы структуры ДУ, поэтому в них также должны обнаруживаться неисправности. Тестеры строятся в виде самопроверяемых устройств с двумя выходами  $Z_1$  и  $Z_2$  (рисунок 5.7) и обозначаются  $m/n$ -СПТ. Они обладают двумя свойствами:

- свойством контроля входного вектора: выходы  $Z_1$  и  $Z_2$  принимают значение (1,0) или (0,1), если на входе тестера присутствует вектор кода  $nSm$ , и значение (0,0) или (1,1), если на вход поступает вектор с весом, отличным от  $m$ ;

- свойством самопроверки: для любой единичной неисправности или любой комбинации одиночных односторонних неисправностей

50

РТМ 32 ЦШ 1115842.01-94

тестера существует входной вектор с весом  $m$ , на котором выходы  $Z_1$  и  $Z_2$  принимают значения (0,0) или (1,1).

Тестер дополняется вполне надежной схемой сравнения (СС), которая непосредственно вырабатывает сигнал контроля при равенстве входных сигналов  $Z_1$  и  $Z_2$  (рисунок 5.7).

Тестеры характеризуются двумя оценками:

- сложностью  $L$ , которая равна суммарному числу входов логических элементов, принадлежащих структуре тестера;

- длиной проверяющего теста  $t$ , которая равна числу слов кода  $nSm$ , подача которых на вход тестера обеспечивает обнаружение всех одиночных и односторонних неисправностей.

## 5.9 Способ описания тестеров

Тестеры описываются системами функций алгебры логики. При этом используется принцип суперпозиции функций. Входные переменные тестера обозначаются цифрами от 1 до  $n$ , соответствующими индексам этих переменных. Для обозначения промежуточных функций, реализуемых на внутренних линиях схемы, также используются цифры от  $n+1$  и далее. Логическая операция дизъюнкции обозначается знаком "+", а операция конъюнкции - знаком "x". Если с помощью конъюнкции связываются два скобочных выражения, то знак "x" опускается.

Промежуточные функции выделяются с таким расчетом, чтобы получаемая при этом система функций полностью отражала структуру схемы тестера. Для этого каждый промежуточный узел разветвления в схеме обозначается отдельной цифрой. Проверяющий тест  $T$  указывается в виде множества слов кода  $nSm$ , заключенных в фигурные скобки.

## 5.10 Каталог тестеров для равновесных кодов

Приведем описание наиболее часто используемых тестеров.

### 5.10.1 1/4-СПТ

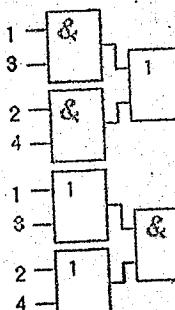

Система функций (рисунок 5.8): 5-1+4, 6-2+3,  $Z_1-(2+5)x$

$\times(4+6)$ ,  $Z_2=(1+6)(3+5)$ . Оценки:  $L=16$ ,  $t=4$ . Тест:  $T=\{1000,01000010,00001\}$ .

## 5.10.2 2/4-СПТ

Система функций (рисунок 5.9):  $Z_1=1\times3+2\times4$ ,  $Z_2=(1+3)(2+4)$ .

Оценки:  $L=12$ ,  $t=4$ . Тест:  $T=\{0101,1001,0110,1010\}$ .

## 5.10.3 1/5-СПТ

Система функций (рисунок 5.10):  $6=1\times2\times5$ ,  $7=1+3$ ,  $8=3+4+5$ ,

$9=2+4$ ,  $Z_1=6\times7+8\times9$ ,  $Z_2=(6+7)(8+9)$ . Оценки:  $L=22$ ,  $t=5$ . Тест:

$T=\{10000,01000,00100,00010,00001\}$ .

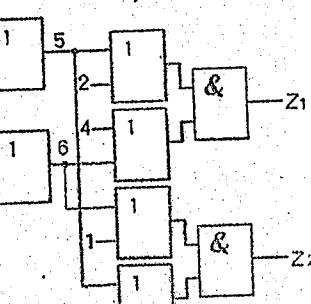

## 5.10.4 2/5-СПТ

Система функций (рисунок 5.11):  $6=1+2$ ,  $7=3+4$ ,  $8=1\times2$ ,  $9=3\times4$ ,

$10=7+6$ ,  $11=5\times7$ ,  $12=9+10$ ,  $13=8+11$ ,  $Z_1=(11+12)(9+13)$ ,  $Z_2=(10+13)\times(8+12)$ . Оценки:  $L=30$ ,  $t=6$ . Тест:  $T=\{10100,01010,01001,00101000,00110\}$ .

## 5.10.5 1/6-СПТ

Система функций:  $7=1+2+5$ ,  $8=1+3+6$ ,  $9=3+4+5$ ,  $10=2+4+6$ ,

$Z_1=7\times8+9\times10$ ,  $Z_2=(7+8)(9+10)$ . Оценки:  $L=24$ ,  $t=6$ . Тест:

$T=\{100000,010000,001000,000100,000010,000001\}$ .

## 5.10.6 2/6-СПТ

Система функций:  $7=2+3$ ,  $8=5+6$ ,  $9=(1+7)(4+8)$ ,  $10=1+4+5$ ,

$11=2\times3+5\times6$ ,  $12=4\times8$ ,  $13=9+12$ ,  $14=10+11$ ,  $Z_1=(10+13)(12+14)$ ,

$Z_2=(9+14)(11+13)$ . Оценки:  $L=36$ ,  $t=7$ . Тест:  $T=\{100100,01001000,001001,110000,011000,0000111,000110\}$ .

## 5.10.7 3/6-СПТ

Система функций:  $7=1\times2$ ,  $8=1+2$ ,  $9=4\times5$ ,  $10=4+5$ ,

$Z_1=(3+8)(9+6\times10)+3\times7$ ,  $Z_2=(6+10)(7+3\times8)+6\times9$ . Оценки:  $L=32$ ,  $t=7$ .

Тест:  $T=\{111000,011100,001110,110001,100011,000111\}$ .

Рисунок 5.11

## 5.11 1/3-СИТ

Тестер для кода "1 из 3" представляет собой особый случай, т. к. он не может быть реализован в виде комбинационной схемы. На рисунке 5.12 представлена схема 1/3-СИТ, построенная в виде схемы с памятью, с характеристиками:  $L = 18$ ,  $t = 5$ .

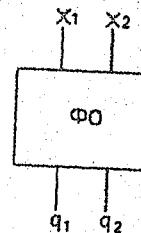

## 5.12 Самопроверяемый фиксатор ошибок

Фиксатор ошибок (ФО) представляет собой устройство (рисунок 5.13), имеющее два входа  $x_1$  и  $x_2$  и два выхода  $q_1$  и  $q_2$ . Вход ФО является парафазным, т. е. допустимыми являются следующие комбинации сигналов  $(x_1, x_2)$ :  $(1, 0)$  -  $(0, 1)$ . Свойства ФО:

- если на вход ФО поступает парафазный сигнал и сама схема ФО исправна, то на его выходе  $(q_1, q_2)$  также присутствует парафазный сигнал -  $(0, 1)$  или  $(1, 0)$ ;

- если на вход ФО в некотором такте его работы поступают одинаковые сигналы  $x_1=x_2$ , то схема ФО блокируется в защитном состоянии и в том же такте на выходе устанавливаются одинаковые сигналы  $q_1=q_2$  ( $0, 0$  или  $1, 1$ ), которые сохраняются во всех последующих тактах работы независимо от состояния входов;

- при возникновении в схеме ФО одиночных неисправностей и любых комбинаций одновременных неисправностей схема также блокируется в защитном состоянии;

- вывод схемы ФО из защитного состояния возможен только в целях установки.

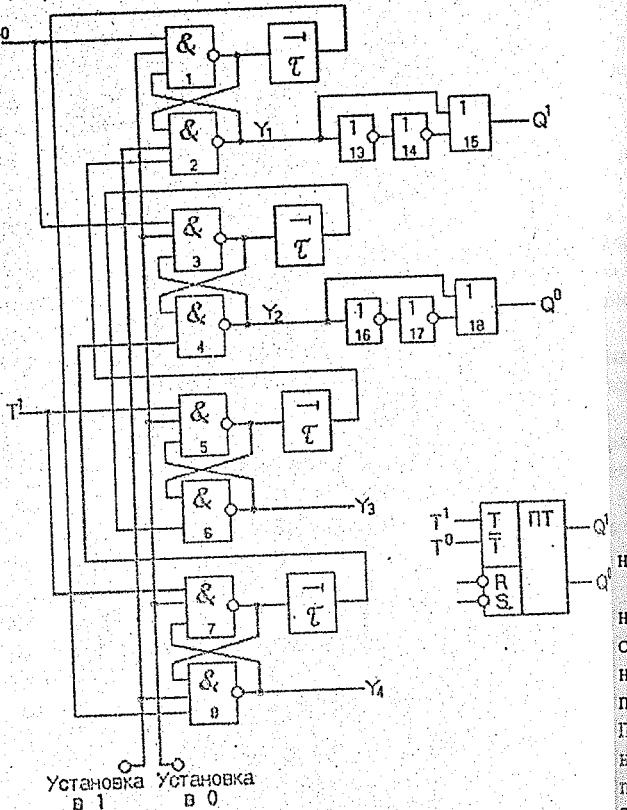

В качестве ФО используются самопроверяющие парафазные триггеры. На рисунке 5.14 представлена схема парафазного асинхронного T-триггера. Он имеет парафазный вход  $T^0T^1$ , парафазный выход  $Q^0$  и работает в соответствии с таблицей переходов 5.12.1.

Схема состоит из четырех бистабильных ячеек и описывается формулами:

$$y_1 = T^0 y_1 \vee T^1 y_1;$$

$$y_2 = T^0 y_2 \vee T^1 y_2;$$

$$y_3 = T^0 y_3 \vee T^1 y_3;$$

Рисунок 5.12

Рисунок 5.13

Рисунок 5.14

| $y_1y_2y_3y_4$ | $T^1T^0$  |           |

|----------------|-----------|-----------|

|                | 01        | 10        |

| 0 1 1 0        | 0110,01   | 1010      |

| 1 0 1 0        | 1001      | (1010),10 |

| 1 0 0 1        | (1001),10 | 0101      |

| 0 1 0 1        | 0110      | (0101),01 |

$$y_4 = T^0y_1 \vee T^1y_4;$$

$$Q^1 = y_1; \quad Q^0 = y_2.$$

Элементы 13, 14, 15 и 16, 17, 18 образуют несимметричные линии задержки, которые исключают непарафазность сигналов  $Q^1$  и  $Q^0$ .

При кратковременной подаче логического нуля на вход "Установка в 0" и наличии сигналов  $T^1T^0=01$  схема приходит в устойчивое состояние 0110 (состояние "0" триггера). При подаче нулевого сигнала на вход "Установка в 1" и наличии сигналов  $T^1T^0 = 01$  схема приходит в устойчивое состояние 1001 (состояние "1" триггера). Полный цикл работы триггера происходит на входной последовательности сигналов  $T^1T^0$  вида 01, 10, 01, 10, 01. При этом схема триггера последовательно проходит все свои состояния: 0110  $\rightarrow$  1010  $\rightarrow$  1001  $\rightarrow$  0101  $\rightarrow$  0110.

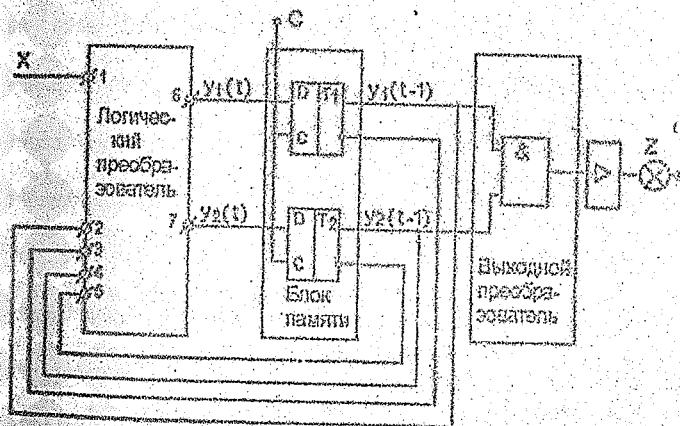

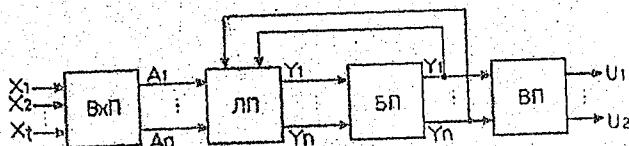

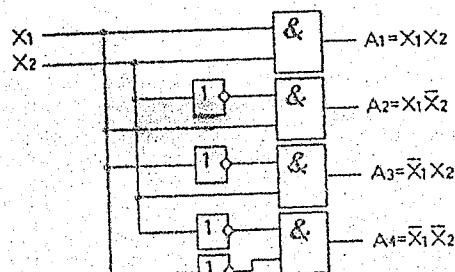

### 5.13 Внутренняя структура самопроверяемого ДУ

Структура ДУ состоит в общем случае из пяти блоков (рисунок 5.15). Блок входного преобразователя ВхII предназначен для реализации наборов входных переменных. Блок логического преобразователя ЛП вычисляет функции включения элементов памяти. Блок памяти

Рисунок 5.15

Рисунок 5.16

Рисунок 5.17

БП содержит все множество элементов памяти (реле, линии задержки, триггеры различного типа). Выходной преобразователь (ВП) предназначен для вычисления выходных функций.

### 5.13.1 Особенности построения блока ВхП

На выходах блока реализуются наборы входных переменных  $x_1, \dots, x_q$ . Каждый набор  $a_1, \dots, a_q$  реализуется отдельной схемой. Пример такого построения приведен на рисунке 5.16 для ДУ, имеющего две входные переменные. В каждый момент времени только на одном выходе блока ВхП может быть сигнал 1.

Возможны три случая проявления одиночных неисправностей на выходах блока ВхП. В первом случае для всех выходов выполняется равенство  $a_j = 0$  ( $j \in \{1, 2, \dots, q\}$ ). Данная неисправность фиксируется блоками ЛП и БП, т. к. при этом на вход блока ЛП поступает вектор с весом  $V = 0$ , тогда как при исправном блоке ВхП поступает вектор с весом  $V = 1$ . Во втором случае имеют место равенства:  $a_j = 1$  и  $a_{t-j} = 1$  ( $j \neq t, j, t \in \{1, 2, \dots, q\}$ ). Данная неисправность также фиксируется блоками ЛП и БП, т. к. при этом на вход блока ЛП поступает вектор с весом  $V = 2$ .

Третий случай имеет место тогда, когда на выходе исправного блока выполняются соотношения  $x_j = 1, x_t = 0$ , а на выходе неисправного блока - соотношения  $x_j = 0, x_t = 1$ . Данная неисправность фиксируется блоками ЛП и БП, т. к. при этом на вход ЛП поступает вектор с весом  $V = 1$ , как и в случае исправного блока ВхП. Такая неисправность возникает при дефектах схемы типа "обрыв входа". В этом случае защита осуществляется введением избыточности в входную информацию. Если входные состояния ДУ закодировать кодом с постоянным весом, то из структуры ВхП исключаются инверторы. Если такое кодирование невозможно, то целесообразно уменьшить вероятность возникновения неисправностей вида "обрыв входа" конструктивными методами или с помощью резервирования.

### 5.13.2 Особенности построения блока ВП

Блок БП представляет собой совокупность элементов памяти.

число элементов памяти определяется длиной кода  $m/n$ , принятого для кодирования внутренних состояний ДУ. Неисправность любого элемента памяти и любое сочетание их односторонних отказов приводит к искажению принятого веса кода состояния, что обнаруживается контрольной схемой  $m/n$ -СПТ.

### 5.13.3 Особенности построения блока ЛП

В блоке ЛП реализуются функции включения элементов памяти. При кодировании состояний ДУ кодом  $m/n$  функции включения являются монотонными. Реализация блока ЛП может быть двух видов - раздельная и совместная. Раздельная реализация предусматривает использование каждого логического элемента в схеме включения только одного элемента памяти. При совместной реализации данное условие может не выполняться. Неисправности блока ЛП оказывают непосредственное влияние на работу элементов памяти и поэтому обнаруживаются из-за искажения вектора состояния внутренних переменных.

### 5.13.4 Особенности реализации блока ВП

В блоке ВП вычисляются выходные функции ДУ. В общем случае отказы элементов ВП не оказывают влияния на работу остальных блоков ДУ и поэтому не могут быть зафиксированы на основании искажения кода внутреннего состояния. Это следует из рисунка 5.15.

Наиболее просто контроль ВП осуществляется по выходному состоянию. В этом случае выходные состояния ДУ дистрибутируются (если это необходимо) путем введения дополнительных контрольных выходов так, чтобы они оказались закодированы кодом с постоянным весом. Функции выходов при этом будут монотонными. Любые комбинации односторонних неисправностей элементов ВП искажают вес выходного состояния.

Второй подход к контролю ВП состоит в полном его совмещении с блоком ЛП. В этом случае элементы блока ВП включаются в цепи обратных связей ДУ, в результате чего их отказы искажают вес кода внутреннего состояния.

### 5.14 Стратегии поведения самопроверяемых дискретных систем

На рисунке 5.17 представлена общая структура самопроверяемого ДУ с внешними схемами контроля. Дискретное устройство имеет рабочие входы  $X_1, \dots, X_n$ , рабочие выходы  $V_1, \dots, V_n$  и контрольные выходы  $Z_1$  и  $Z_2$ , которые формируются самопроверяемым тестером  $m/n$ -СПТ. Нарушение параллельности выходов  $Z_1$  и  $Z_2$  регистрируется ПСП-схемой фиксатора ошибок (ФО), играющей роль "последнего сторожа". При нарушении параллельности выходов ФО блокируется в защитном состоянии, при котором нарушается параллельность его выходов и которое не зависит от последующего изменения входов. ФО включает индикатор отказа системы (ИО). После восстановления исправности ДУ фиксатор ошибки переводится по цепи установки в рабочее состояние. В качестве ФО может быть использован любой ПСП-триггер.

В безопасных системах при возникновении отказа и блокировке ФО возможны три стратегии в поведении ДУ:

- отключение всей системы;

- повторный запуск фиксатора ошибок;

- отключение рабочих выходов.

В первом случае организуется самопроверяемая обратная связь, когда выходы ФО подключаются к специальным тактовым входам  $\Phi 1$  и  $\Phi 2$  дискретного устройства. При нарушении параллельности на входах  $\Phi 1$  и  $\Phi 2$  отключается тактовое питание системы и ДУ преводится в защитное состояние. Другой способ отключения системы состоит в коммутации цепей питания на контактах специального контрольного реле, обмотка которого подключается к выходам ФО через самопроверяемые схемы включения реле ССВР (они описаны в разделе 7).

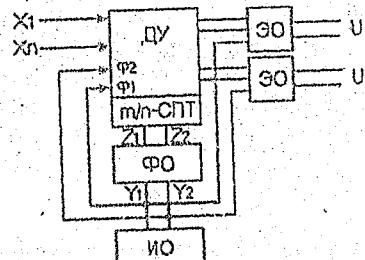

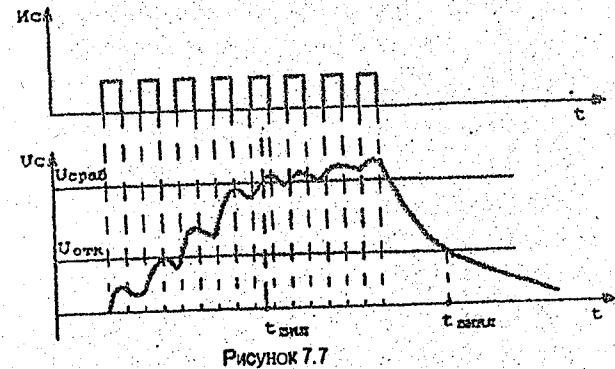

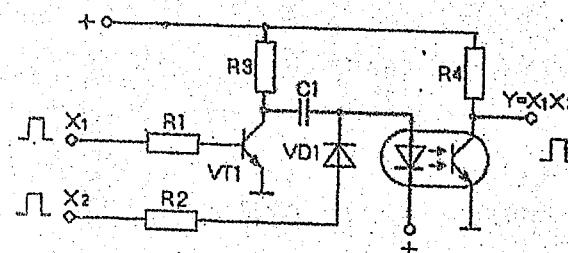

Рисунок 5.18 иллюстрирует вторую стратегию поведения ДУ при отказе - повторный запуск ФО. Эта стратегия применяется для повышения устойчивости дискретной системы относительно сбоев. Для включения реле К используется схема формирования импульсных сигналов. В ней выходы  $m/n$ -СПТ, на которых может длительно сохраняться статический параллельный сигнал, подключаются ко входам 2/4-СПТ. На другие входы 2/4-СПТ поступают параллельные импульсы от тактового генератора. При этом на выходе 2/4-СПТ формируется импульсный параллельный сигнал. Если в результате случайного сбоя на

Рисунок 5.18

Рисунок 5.19

РТМ 32 ЦШ 1115842.01-94

выходе  $m/n$ -СПТ нарушается парофазность сигналов, то блокируются триггеры  $T_1$  и  $T_2$ . На выходах  $T_2$  устанавливаются одинаковые сигналы и происходит запуск одновибратора  $S$ , который через некоторое время вырабатывает сигнал на установку  $\Phi\text{O}$  в рабочее состояние. Это время меньше, чем время отпускания реле  $K$ , поэтому в момент установки  $\Phi\text{O}$  питание системы еще не отключено.

Если действие сбоя было кратковременным и парофазность сигналов на выходе  $m/n$ -СПТ восстановилась, то после окончания сигнала установки триггер  $T_1$  остается в рабочем состоянии, продолжает работу  $\Phi\text{CVR}$  и реле  $K$  снова получает питание. Нормальное функционирование  $\text{ДУ}$  продолжается. В противном случае после окончания сигнала установки триггер  $T_1$  снова блокируется, реле  $K$  отпускает якорь и выключает питание системы. Установка триггера  $T_2$  в рабочее состояние происходит уже после завершения описанных процессов, что обеспечивается специальным генератором восстановления ( $\text{ГВ}$ ) с низкой частотой работы.

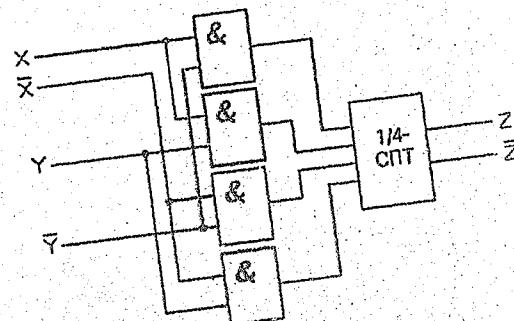

Третья стратегия поведения  $\text{ДУ}$  при отказах состоит в отключении рабочих выходов. При этом парофазные выходные сигналы  $\text{ДУ}$  (рисунок 5.17) транслируются через специальные самопроверяемые элементы сравнения  $\mathcal{E}\text{O}$  (рисунок 5.19). Схема  $\mathcal{E}\text{O}$  имеет парофазный информационный вход ( $X, \bar{X}$ ), который подключается к выходу  $\text{ДУ}$ , и парофазный контрольный вход ( $Y, \bar{Y}$ ), связанный с выходами  $\Phi\text{O}$ . Парофазный выход ( $Z, \bar{Z}$ ) повторяет значение сигнала ( $X, \bar{X}$ ), если на входе ( $Y, \bar{Y}$ ) имеется парофазный сигнал. В противном случае парофазность на выходе нарушается. Таким образом, при возникновении отказа и блокировке  $\Phi\text{O}$  в защищном состоянии схемы  $\mathcal{E}\text{O}$  отключают выходы  $\text{ДУ}$  от нагрузки. Все три описанные стратегии могут быть использованы и одновременно, что обеспечивает высокий уровень безопасности, т. е. высокую вероятность отсутствия неправильного воздействия на объекты управления.

6 ПРОГРАММНЫЕ МЕТОДЫ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ СИСТЕМ

ЖЕЛЕЗНОДОРОЖНОЙ АВТОМАТИКИ

6.1 Методы обеспечения надежности программных средств

Требование высокой надежности является первостепенным при проектировании систем железнодорожной автоматики. Построение таких систем на базе программируемой аппаратуры (ПУА) порождает свою специфику в постановке и решении задач обеспечения высокой надежности. Эта специфика определяется тем, что специализация ПУА под конкретные технологические задачи производится программным способом. Программные средства в этом случае являются определяющими в реализации системой требуемых функций.

Согласно [6.1], под надежностью понимают свойство объекта сохранять во времени в установленных пределах значения всех параметров, характеризующих способность системы выполнять требуемые функции в заданных режимах и условиях применения. Применительно к безопасным СЖАТ под выполнением заданных функций следует понимать комплекс:

- функций, обеспечивающих реализацию технологических алгоритмов с учетом проверки условий обеспечения безопасности движения поездов;

- функций, определяющих поведение системы в условиях возникновения отказов и сбоев технических средств или проявления программных ошибок.

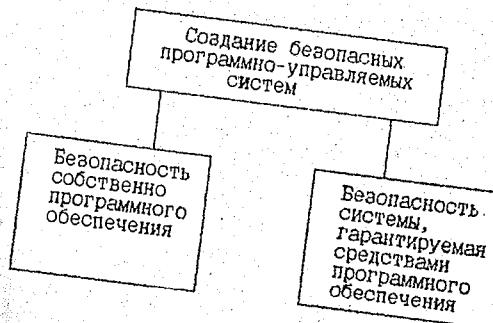

Таким образом, создание безопасных систем, логика функционирования которых отражена в виде программы, охватывает два аспекта (рисунок 6.1), в соответствии с которыми процесс создания безопасного программного обеспечения предусматривает комплекс мероприятий, направленных на:

- корректную постановку целевых функций системы;

- корректную программную интерпретацию целевых функций системы.

С точки зрения обеспечения безопасности актуальным является решение как первой, так и второй задачи. Например, правильно сформулированные функции программно-управляемой системы могут

Рисунок 6.1

РТМ 32 ЦШ 1115842.01-94

быть небезопасными в результате ошибки программиста или ошибочных средств трансляции. И наоборот, корректно выраженные в виде программы функции системы могут содержать ошибки функционального характера или быть функционально неполными в охвате последствий отказов.

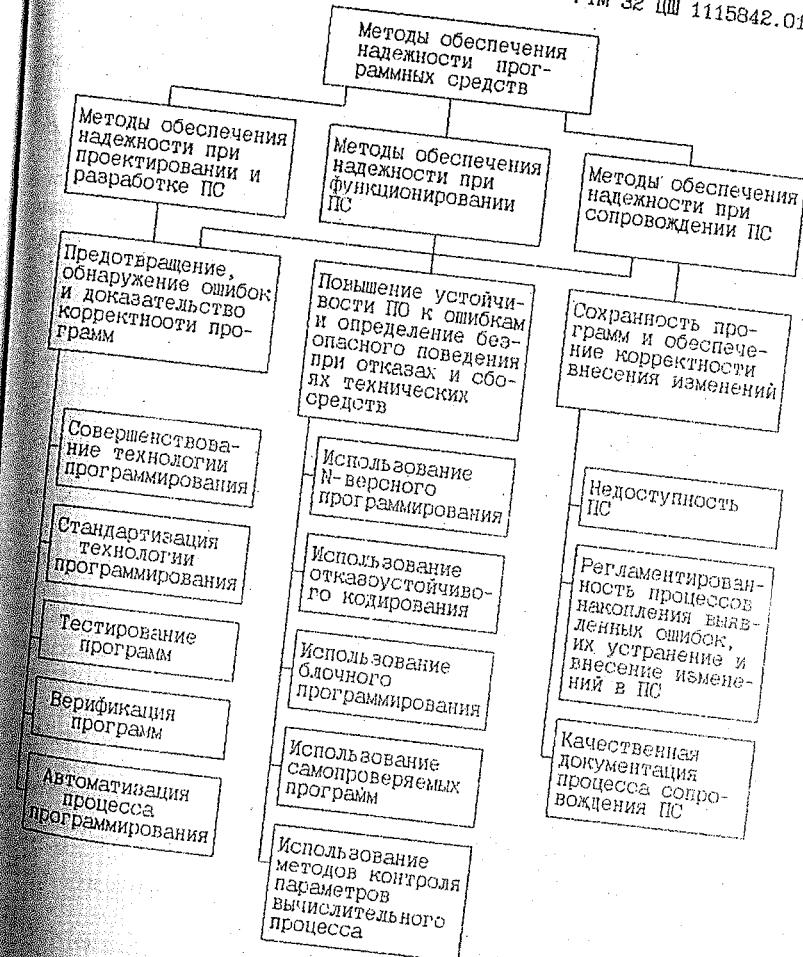

Опыт разработки программных средств систем управления технологическими процессами, критичными к вопросам безопасности, показывает, что проблема обеспечения надежности программных средств (ПС) охватывает все этапы жизненного цикла программ (рисунок 6.2). Такое разнообразие методов определяется тем, что существует принципиальное различие в причинах нарушения работоспособности программных средств.

Одной из причин нарушения работоспособности программных средств является отклонение исходного текста программ от формализованного эталона и требований заказчика. Ошибки такого рода в практике программирования получили название ошибок программирования, возникающих в основном при разработке ПО и его сопровождении. В литературе рассматривается широкий спектр организационных и технических мероприятий по их предотвращению и обнаружению, которые позволяют выделить основные пути повышения надежности функционирования программных средств [6.2], такие как: